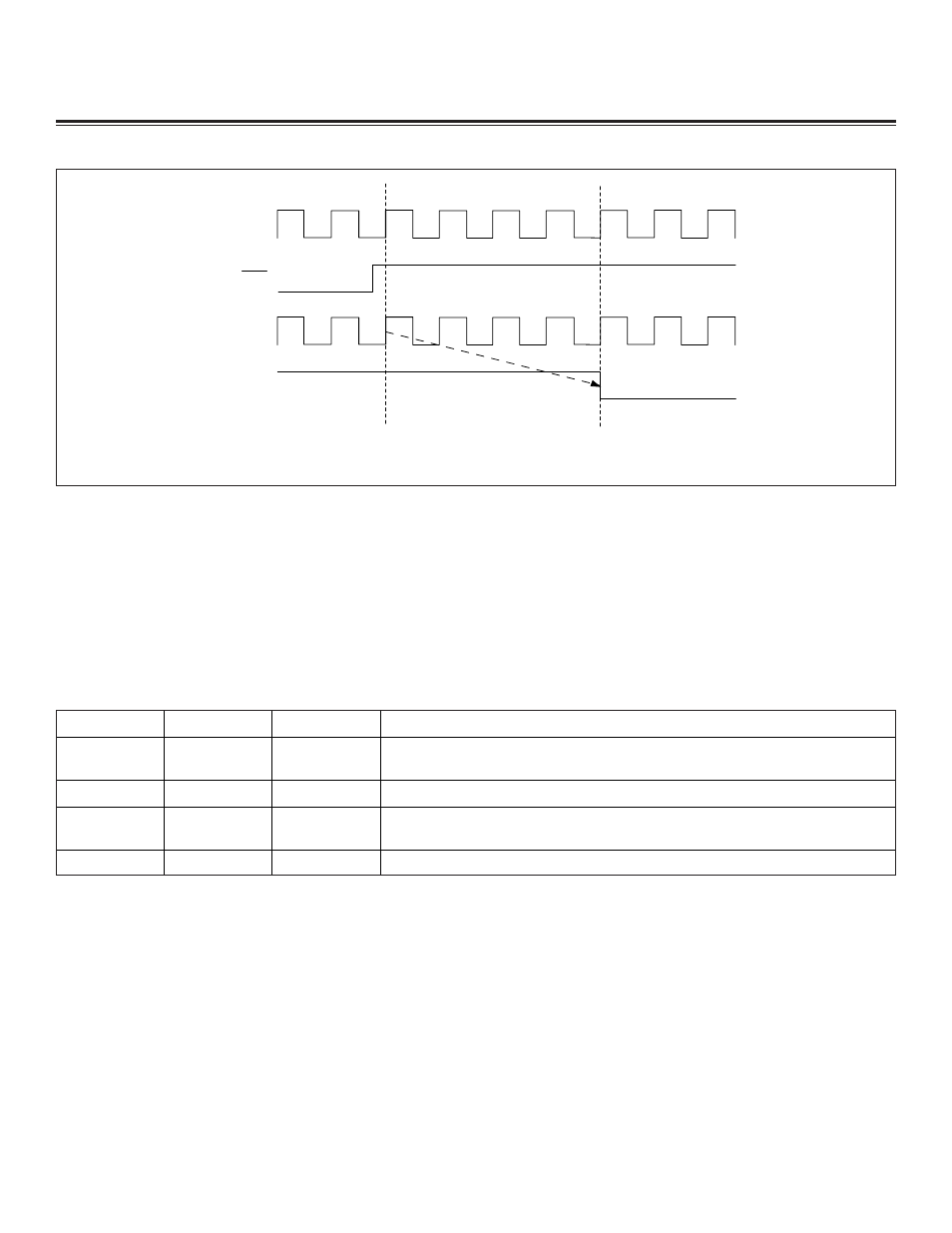

Figure 7. maxq2000 external reset, Table 3. system power management registers, Power management features – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 17: Divide-by-256 mode (pmm1), Maxq family user’s guide: maxq2000 supplement

Power Management Features

The MAXQ2000 provides the following features to assist in power management.

• Divide-by-256 (PMM1) and 32kHz (PMM2) modes to reduce current consumption.

• Switchback mode to exit PMM modes automatically when rapid processing is required.

• Ultra-low-power Stop mode.

Table 3 shows the system registers and bits used to control power management features. For more information, refer to the register

descriptions in the MAXQ Family User’s Guide.

Table 3. System Power Management Registers

Divide-by-256 Mode (PMM1)

In this power management mode, all operations continue as normal but at a reduced clock rate (the high-frequency system clock divid-

ed by 256). This power management mode affects module clock rates as follows.

• Program execution occurs at the high-frequency clock rate divided by 256.

• The RTC module continues to operate using its originally selected clock, which is either the 32kHz clock or the high-frequency clock

divided by 128, as selected by the ACS bit (RCNT.13).

• The LCD module continues to operate using its originally selected clock, which is either the 32kHz clock or the high-frequency clock

divided by 128, as selected by the LCCS bit (LCRA.6).

• All other functional modules (timers, UARTs, SPI) operate at the high-frequency clock rate divided by 256.

MAXQ Family User’s Guide:

MAXQ2000 Supplement

CLOCK

RESET

RESET

SAMPLING

INTERNAL

RESET

FIRST

INSTRUCTION

FETCH

Figure 7. MAXQ2000 External Reset

REGISTER

ADDRESS

BIT

FUNCTION

CKCN

M8[0Eh]

[1:0] to CD[1:0]

Selects clock divide-by-1 (00), -2 (01), -4 (10), or -8 (11) mode. When PMM mode is

enabled, selects divide-by-256 (00) or 32kHz (11) mode.

CKCN

M8[0Eh]

2 (PMME)

Selects PMM mode (when set to 1) or normal clock divide mode (when set to 0).

CKCN

M8[0Eh]

3 (SWB)

When set to 1, enables automatic switchback from PMM (divide-by-256 mode) to normal

clock divide mode under certain conditions.

CKCN

M8[0Eh]

4 (STOP)

When set to 1, causes the processor to enter Stop mode.

Maxim Integrated

17