Reset conditions, Power-on reset, Watchdog timer reset – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 16: External reset, Figure 6. maxq2000 power-on reset, Maxq family user’s guide: maxq2000 supplement

MAXQ Family User’s Guide:

MAXQ2000 Supplement

Reset Conditions

There are three possible reset sources for the MAXQ2000. While in the reset state, the enabled system clock oscillator continues run-

ning, but no code execution occurs. Once the reset condition has been removed or has completed, code execution resumes at

address 8000h for all reset types.

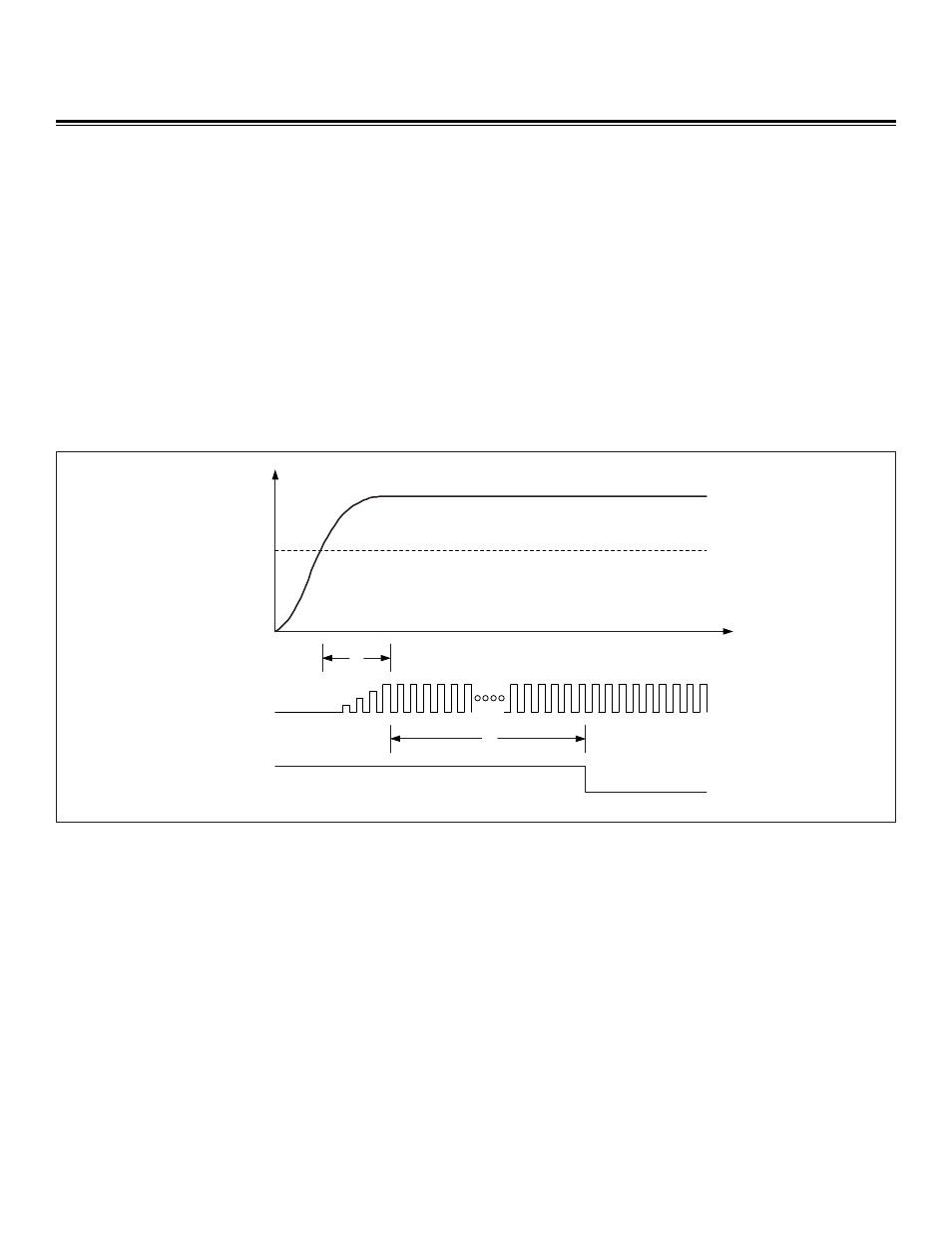

Power-On Reset

When power is first applied to the MAXQ2000, or when the internal supply voltage V

DD

drops below the minimum allowed value, the

processor is held in a power-on reset state (Figure 6). For the MAXQ2000 to exit power-on reset, the following two conditions must apply:

• V

DD

is within the acceptable range for that power supply (see data sheet for values).

• The ring oscillator has completed 65,536 cycles (delay for power supply to stabilize).

Note that since the MAXQ2000 has no brownout reset function, the power-on reset is only guaranteed to occur if V

DD

drops all the way

to ground before rising again. Brownout events where V

DD

drops partially (but remains above ground) and then rises back into the

acceptable range are not guaranteed to trigger a power-on reset and can result in unpredictable device behavior.

If the V

DDIO

power supply drops to ground, a power-on reset is not triggered. However, this causes all port pins driven by V

DDIO

to

drop to ground. Additionally, the 32kHz oscillator only operates when V

DDIO

is within acceptable limits.

Watchdog Timer Reset

The watchdog timer on the MAXQ2000 functions as described in the MAXQ Family User’s Guide. When running at 14MHz, the maxi-

mum watchdog time period before reset is approximately 150ms.

Since the RGSL bit is cleared to 0 on power-on reset only, it is possible to exit a watchdog reset with the clock source set to the high-

frequency oscillator. In this case, execution resumes running from the ring oscillator, and the switchover to the high-frequency oscilla-

tor occurs automatically when the 65,536-cycle warmup delay for that oscillator has completed.

External Reset

External reset via

RESET is a synchronous reset source. After the external reset low has been removed and sampled, execution

resumes (running from the ring oscillator) following a delay of four ring-oscillator cycles, as shown in Figure 7.

Since the RGSL bit is cleared to 0 on power-on reset only, it is possible to exit an external reset with the clock source set to the high-

frequency oscillator. In this case, execution resumes running from the ring oscillator, and the switchover to the high-frequency oscilla-

tor occurs automatically when the 65,536-cycle warmup delay for that oscillator has completed.

V

DD(MIN)

T1

RING

OSCILLATOR

INTERNAL

RESET

T2

(T1 = STARTUP TIME FOR RING OSCILLATOR)

(T2 = 65,536 RING OSCILLATOR CYCLES, OR 8.192ms AT 8MHz)

Figure 6. MAXQ2000 Power-On Reset

Maxim Integrated

16