Wire example: reset and presence detect, Addendum to section 14: real-time clock module, Table 24. real-time clock control registers – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 55: Maxq family user’s guide: maxq2000 supplement

1-Wire Example: Reset and Presence Detect

OW_COMMAND equ 00h

OW_BUFFER equ 01h

OW_INTERRUPT equ 02h

OW_INT_ENABLE equ 03h

OW_CLOCK equ 04h

OW_CONTROL equ 05h

move OWA, #OW_CLOCK

; Access 1-Wire Clock Control Register

move OWD, #10001001b

; Divide ratio = 12, enable clock

move OWA, #OW_CONTROL

; Access 1-Wire Control Register

move OWD, #00h

; Clear register

Reset:

move OWA, #OW_COMMAND

; Access 1-Wire Command Register

move OWD, #01h

; Initiate 1-Wire reset cycle

move LC[0], #60000

djnz LC[0], $

; Delay

move OWA, #OW_INTERRUPT

; Access 1-Wire Interrupt Flag Register

move Acc, OWD

; Get interrupt flags

move C, Acc.0

; Check PD flag (1=reset cycle completed)

jump NC, Reset

; Retry

move C, Acc.1

; Get presence detect result (0=found slave device)

ADDENDUM TO SECTION 14: REAL-TIME CLOCK

The MAXQ2000 provides a real-time clock that operates as described in the MAXQ Family User’s Guide. Table 24 shows the associ-

ated registers for this module.

Real-Time Clock Example: Starting and Setting the Clock

move RCNT, #00000h

; Turn on 32kHz crystal oscillator

move RCNT, #08000h

; RTC write enable

move RTSS, #00h

; Clear sub-second count

move RTSL, #0000h

; Clear low-order seconds counter

move RTSH, #0000h

; Clear high-order seconds counter

move RCNT, #08001h

; Start clock

MAXQ Family User’s Guide:

MAXQ2000 Supplement

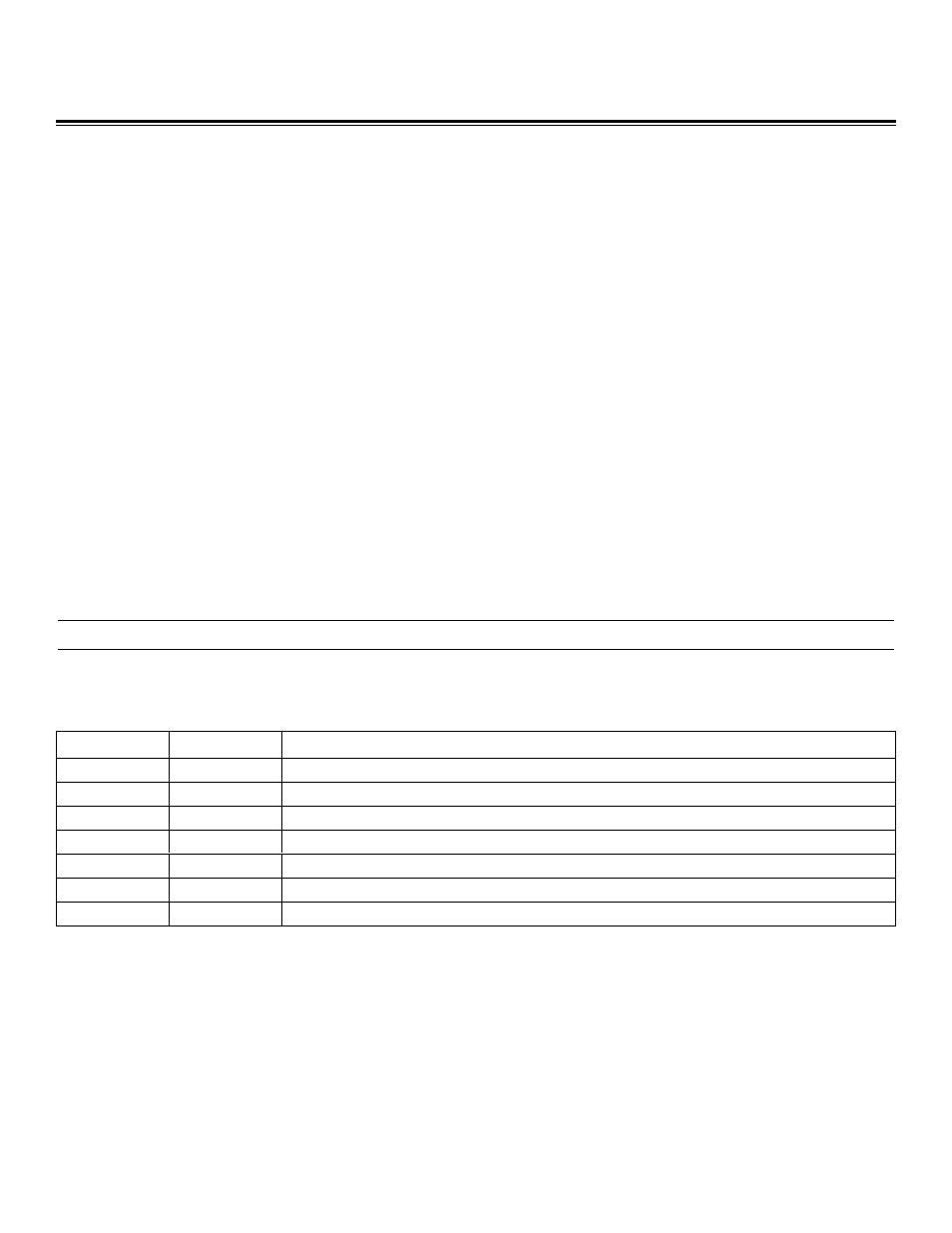

REGISTER

ADDRESS

FUNCTION

RCNT

M0[19h]

Real-Time Clock Control Register. Sets modes and alarm enables for the clock.

RTSS

M0[1Ah]

RTC Sub-Second Counter Register. Contains the 1/256 sub-second count.

RTSL

M0[1Ch]

RTC Second Counter Low Register. Contains the low-order byte of the 32-bit second count.

RTSH

M0[1Bh]

RTC Second Counter High Register. Contains the high-order byte of the 32-bit second count.

RSSA

M0[1Dh]

RTC Sub-second Alarm Register. Contains the sub-second alarm reload value.

RASL

M0[1Fh]

RTC Time-of-Day Alarm Low Register. Contains the low-order 16 bits of the time-of-day alarm value.

RASH

M0[1Eh]

RTC Time-of-Day Alarm High Register. Contains the high-order 8 bits of the time-of-day alarm value.

Table 24. Real-Time Clock Control Registers

Maxim Integrated

55