Maxq family user’s guide: maxq2000 supplement, Lcd duty cycle and bias mode selection – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 68

Register Name:

LCRA

Register Description:

LCD Adjust Register

Register Address:

M2[0Dh]

This register can only be written to when the LCD controller is in suspended mode (OPM = 0).

Bits 0 to 4: (LCRA.0 to LCRA.4) LCD Register Adjust (LRA0 to LRA4). These bits control the resistance of the internal LCD resis-

tor R

ADJ

. The approximate resistance can be determined as follows.

if (LRA[4:0] = 0), R

ADJ

= 200kΩ

if (LRA[4:0] > 0), R

ADJ

= (LRA[4:0] - 1) x 6.45kΩ

Bit 5: (LCRA.5) LCD Resistor Internally Grounded (LRIG)

0 = R

ADJ

is disconnected from ground internally.

1 = R

ADJ

is connected to ground internally.

Bit 6: (LCRA.6) LCD Clock Select (LCCS). This bit selects the source clock (f

LCD

) used for LCD segment and common timing gen-

eration.

0 = f

LCD

= 32kHz clock

1 = f

LCD

= high-frequency oscillator / 128

Bits 7 to 10: (LCRA.7 to LCRA.10) LCD Frame Frequency (FRM0 to FRM3). These bits select the LCD frame frequency as follows.

for 1/3 bias mode: f

FRAME

= f

LCD

/ [(FRM[3:0]) + 1) x 96]

for all other modes: f

FRAME

= f

LCD

/ [(FRM[3:0]) + 1) x 64]

Bits 11 and 12: (LCRA.11 and LCRA.12) LCD Duty Cycle Select (DUTY0 and DUTY1). These bits select the LCD duty cycle and

corresponding bias generation mode as follows.

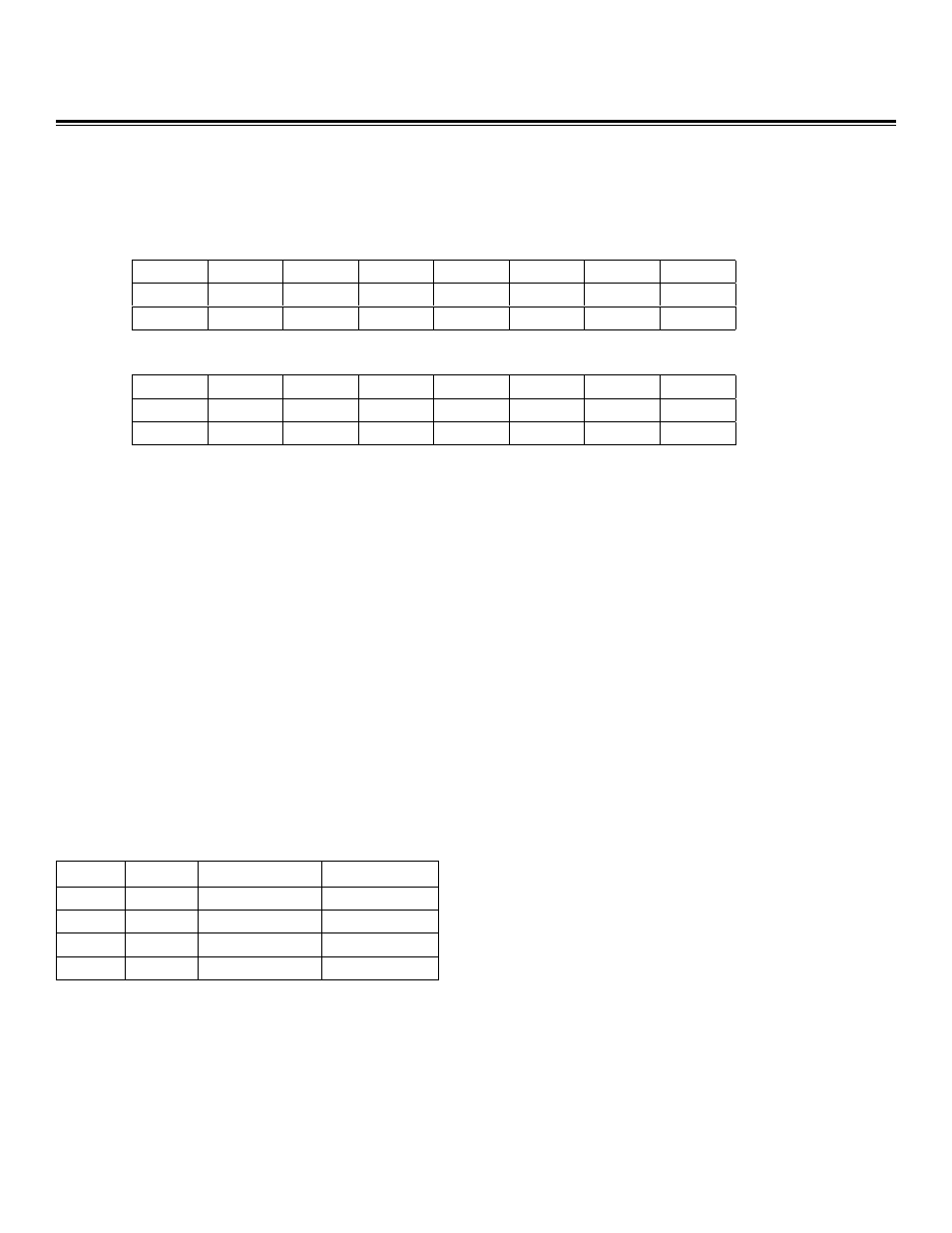

LCD Duty Cycle and Bias Mode Selection

Bits 13 to 15: (LCRA.13 to LCRA.15) Reserved

DUTY1

DUTY0

DUTY CYCLE

BIAS MODE

0

0

Static

Static

0

1

1/2

1/2

1

0

1/3

1/3

1

1

1/4

1/3

MAXQ Family User’s Guide:

MAXQ2000 Supplement

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

DUTY1

DUTY0

FRM3

FRM2

FRM1

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r/w

r/w

r/w

r/w

r/w

Bit #

7

6

5

4

3

2

1

0

Name

FRM0

LCCS

LRIG

LRA4

LRA3

LRA2

LRA1

LRA0

Reset

0

0

0

0

0

0

0

0

Access

r/w

r/w

r/w

r/w

r/w

r/w

r/w

r/w

Maxim Integrated

68