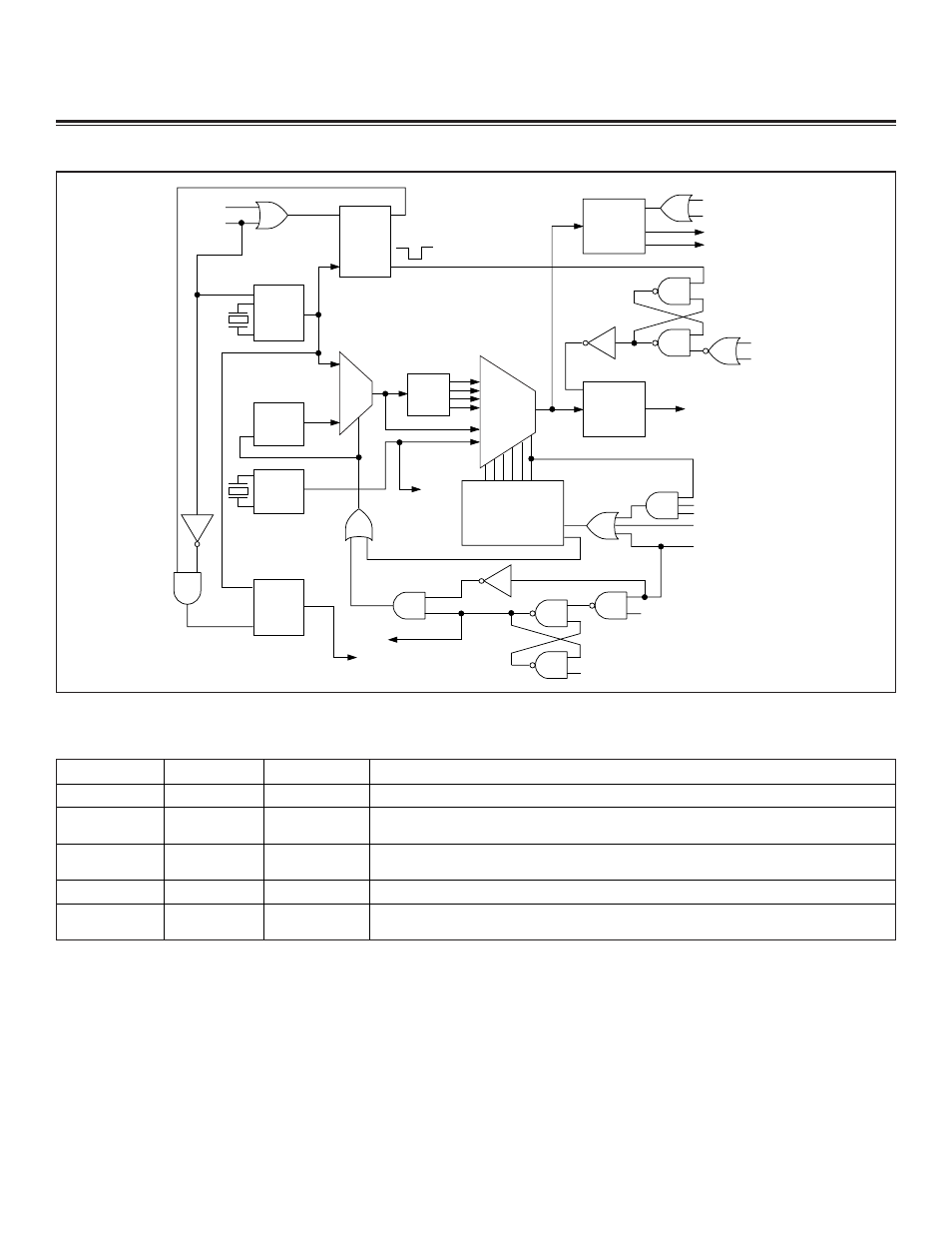

Internal ring oscillator, Figure 5. maxq2000 clock sources, Maxq family user’s guide: maxq2000 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 12

MAXQ Family User’s Guide:

MAXQ2000 Supplement

Table 1. System Clock Generation and Control Registers

External High-Frequency Oscillator Circuit or Clock

The high-frequency oscillator is the default source for system clock generation. This oscillator operates as described in the “Clock

Generation” section of Section 2: Architecture in the MAXQ Family User’s Guide. When using an external crystal or resonator circuit,

the circuit should be connected between the HFXIN and HFXOUT. When using an external clock signal to drive the high-frequency

clock, the external clock signal should be connected to the HFXIN pin, and the HFXOUT pin should be left unconnected.

Internal Ring Oscillator

The MAXQ2000 provides an internal ring oscillator that can be used as an alternate source for the system clock. This oscillator, which

requires no external components, typically runs at an 8MHz frequency. The exact frequency of the ring oscillator is not fixed and will

vary from part to part due to process variations, as well as over temperature and supply voltage for any given part.

REGISTER

ADDRESS

BIT

FUNCTION

CKCN

M8[0Eh]

[1:0] to CD[1:0]

Selects clock divide-by-1 (00), -2 (01), -4 (10), or -8 (11) mode.

CKCN

M8[0Eh]

2 (PMME)

If set to 0, selects normal clock divide mode (as determined by CD[1:0]). If set to 1, selects

either divide-by-256 mode (when CD[1:0]=00) or 32kHz mode (when CD[1:0]=11).

CKCN

M8[0Eh]

5 (RGMD)

Read-only. Indicates if ring oscillator (1) or external crystal/clock (0) is being used to provide

the system clock.

CKCN

M8[0Eh]

6 (RGSL)

Selects ring oscillator (1) or external crystal/clock (0) as the clock source.

RCNT

M0[19h]

14 (X32D)

Disables (1) or enables (0) the internal 32kHz oscillator. If the 32kHz oscillator is disabled,

the RTC can be driven externally by a 32kHz clock input signal.

MAXQ2000

GLITCH-FREE

MUX

GLITCH-FREE

MUX

DIV 1

DIV 2

DIV 4

DIV 8

32kHz

PMM

CLOCK

DIVIDER

SELECTOR

WAKE-UP

ALARM

TIMERS

DEFAULT

RING SELECT

WATCHDOG

TIMER

RESET DOG

RWT

RESET

POWER-ON

RESET

STOP

STOP

POWER-ON

RESET

SWB

INTERRUPT/SERIAL PORT

RESET

STOP

RGSL

XDOG DONE

RGMD

POWER-ON RESET

WATCHDOG RESET

CLOCK

GENERATION

SYSTEM CLOCK

ENABLE

WATCHDOG INTERRUPT

RING

ENABLE

32kHz

CRYSTAL

CRYSTAL

MONITOR

ENABLE

INPUT

HF

CRYSTAL

CRYSTAL KLL

XDOG

STARTUP

TIMER

CLK INPUT

RESET

XDOG COUNT

XDOG DONE

Figure 5. MAXQ2000 Clock Sources

Maxim Integrated

12