Maxq family user’s guide: maxq2000 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 38

MAXQ Family User’s Guide:

MAXQ2000 Supplement

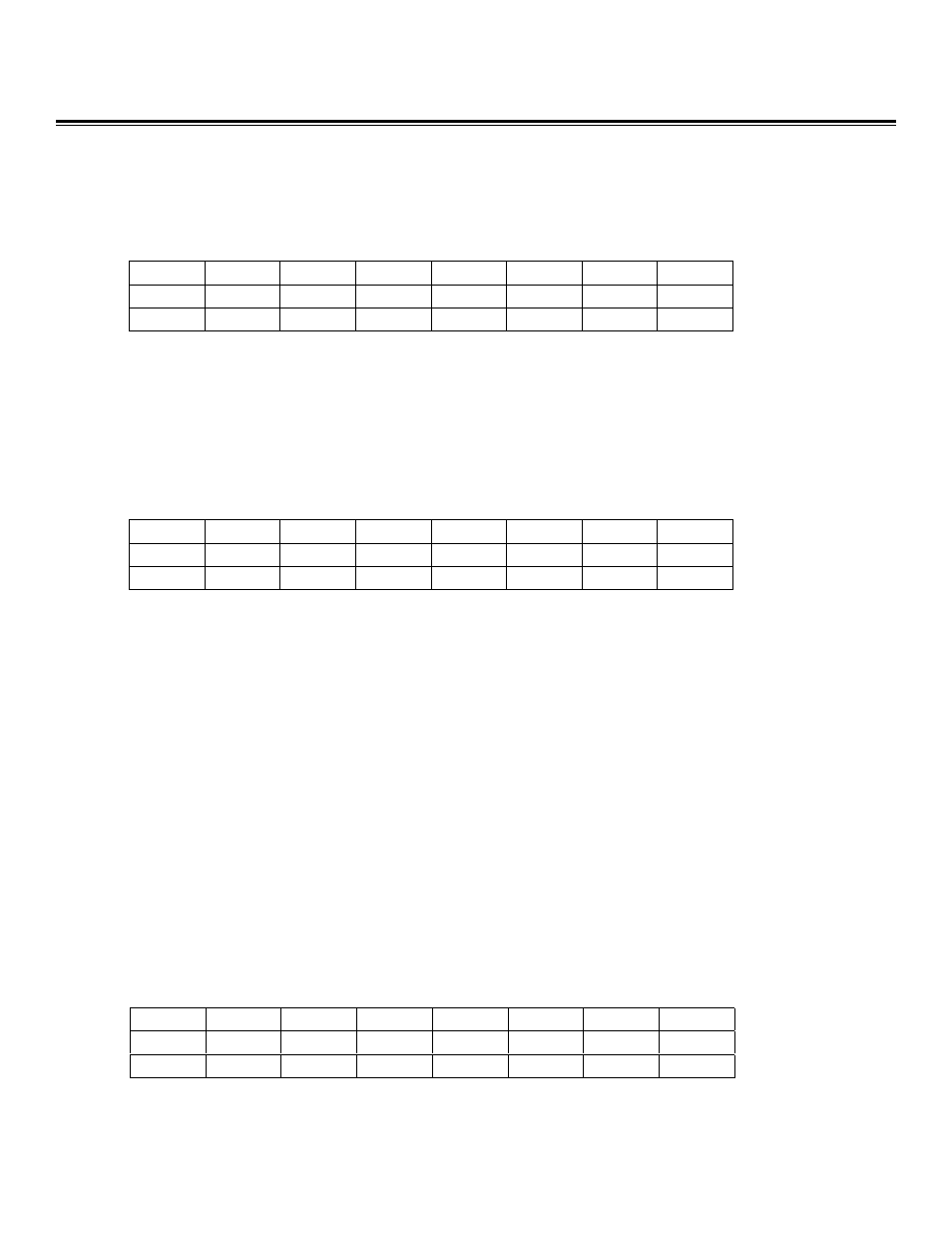

Register Name:

PO3

Register Description:

Port 3 Output Register

Register Address:

M0[03h]

Bits 0 to 7: (PO3.0 to PO3.7) Port 3 Output. This register stores the data that will be output on any of the pins of Port 3 that have been

defined as output pins. If the port pins are in input mode, this register controls the weak pullup for each pin. Changing the data direc-

tion of any pins for this port (through register PD3) will not affect the value in this register.

Register Name:

EIF0

Register Description:

External Interrupt Flag 0 Register

Register Address:

M0[06h]

Each bit in this register is set when a negative or positive edge (depending on the ITn bit setting) is detected on the corresponding

interrupt pin. Once an external interrupt has been detected, the interrupt flag bit will remain set until cleared by software or a reset.

Setting any of these bits will cause the corresponding interrupt to trigger if it is enabled to do so.

Bit 0: (EIF0.0) External Interrupt 0 Edge Detect (IE0)

Bit 1: (EIF0.1) External Interrupt 1 Edge Detect (IE1)

Bit 2: (EIF0.2) External Interrupt 2 Edge Detect (IE2)

Bit 3: (EIF0.3) External Interrupt 3 Edge Detect (IE3)

Bit 4: (EIF0.4) External Interrupt 4 Edge Detect (IE4)

Bit 5: (EIF0.5) External Interrupt 5 Edge Detect (IE5)

Bit 6: (EIF0.6) External Interrupt 6 Edge Detect (IE6)

Bit 7: (EIF0.7) External Interrupt 7 Edge Detect (IE7)

Register Name:

EIE0

Register Description:

External Interrupt Enable 0 Register

Register Address:

M0[07h]

Each bit in this register controls the enable for one external interrupt. If the bit is set to 1, the interrupt is enabled (if it is not otherwise

masked). If the bit is set to 0, its corresponding interrupt is disabled.

Bit #

7

6

5

4

3

2

1

0

Name

PO3.7

PO3.6

PO3.5

PO3.4

PO3.3

PO3.2

PO3.1

PO3.0

Reset

1

1

1

1

1

1

1

1

Access

r/w

r/w

r/w

r/w

r/w

r/w

r/w

r/w

Bit #

7

6

5

4

3

2

1

0

Name

EX7

EX6

EX5

EX4

EX3

EX2

EX1

EX0

Reset

0

0

0

0

0

0

0

0

Access

r/w

r/w

r/w

r/w

r/w

r/w

r/w

r/w

Bit #

7

6

5

4

3

2

1

0

Name

IE7

IE6

IE5

IE4

IE3

IE2

IE1

IE0

Reset

0

0

0

0

0

0

0

0

Access

r/w

r/w

r/w

r/w

r/w

r/w

r/w

r/w

Maxim Integrated

38