Section 18.3.3.6, “cfmdacc, Cfm data access register, 6 cfmdacc — cfm data access register – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 303: 7 cfmustat — cfm user status register

ColdFire Flash Module (CFM)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

18-13

18.3.3.6

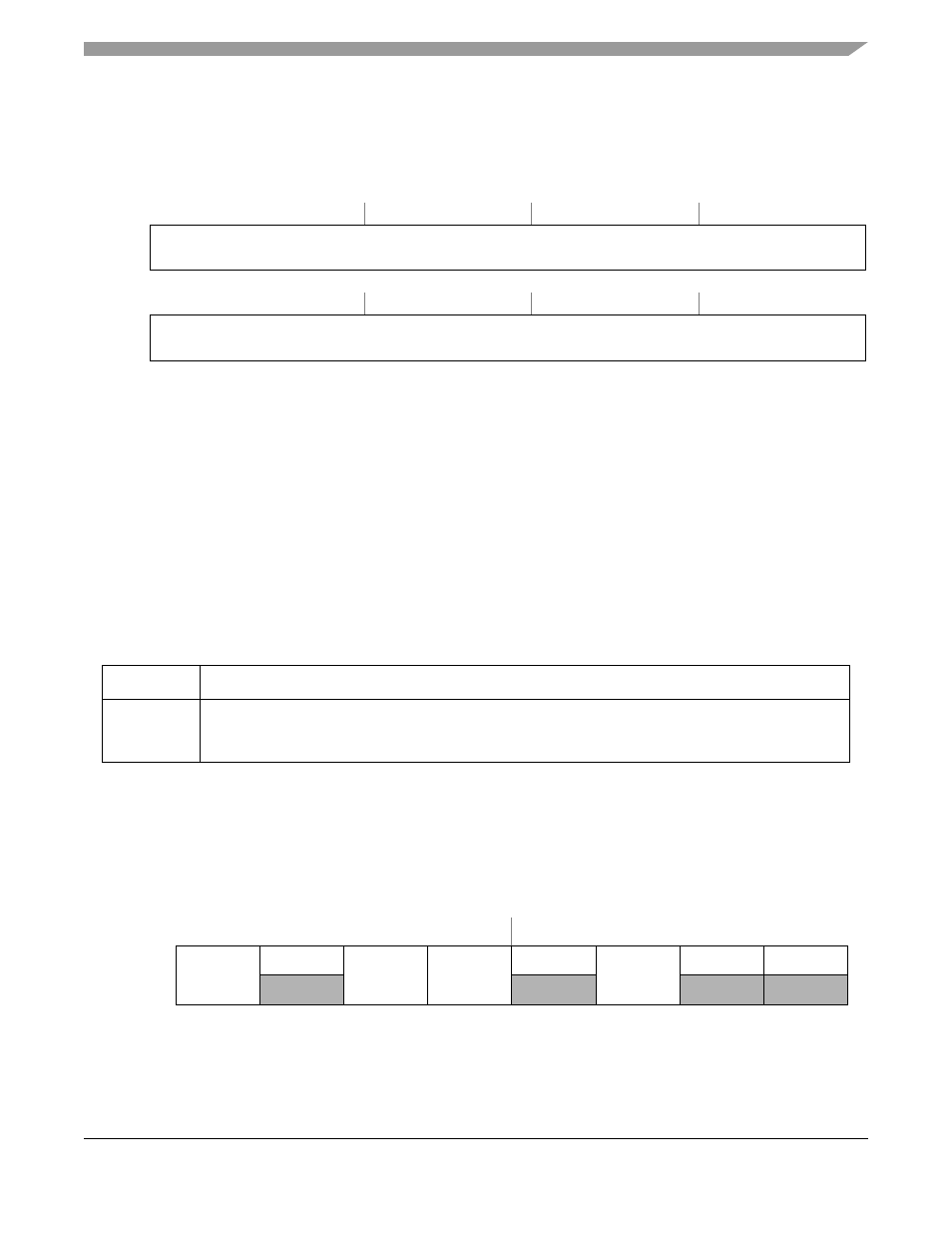

CFMDACC — CFM Data Access Register

The CFMDACC register is used to control data/instruction access to the flash memory.

Figure 18-10. CFM Data Access Register (CFMDACC)

All CFMDACC register bits are readable and only writable when LOCK=0.

To change the flash data access on a temporary basis, the CFMDACC register should be written after the

LOCK bit in the CFMMCR register has been cleared. To change the flash data access loaded during the

reset sequence, the flash logical sector containing the flash configuration field must first be unprotected,

and then the flash data access bytes must be programmed with the desired value. Each flash logical sector

may be mapped into data or both data and instruction address space (see

sector mapping).

18.3.3.7

CFMUSTAT — CFM User Status Register

The CFMUSTAT register defines the flash command controller status and flash memory access, protection

and verify status.

Figure 18-11. CFM User Status Register (CFMUSTAT)

IPSBAR

Offset: 0x1D_0018 (CFMDACC)

Access: User read/write

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

DACC

W

Reset

F

1

1

Reset state loaded from flash configuration field during reset.

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

DACC

W

Reset

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

F

1

Table 18-10. CFMDACC Field Descriptions

Field

Description

31 - 0

DACC

Flash memory address space assignment for data/instruction access

DACC[M] = 1: Flash logical sector M is placed in data address space.

DACC[M] = 0: Flash logical sector M is placed in data and instruction address space.

IPSBAR

Offset: 0x1D_0020 (CFMUSTAT)

Access: User read/write

7

6

5

4

3

2

1

0

R

CBEIF

CCIF

PVIOL

ACCERR

0

BLANK

0

0

W

Reset:

1

1

0

0

0

0

0

0