2 eport data direction register (epddr), 3 edge port interrupt enable register (epier) – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 272

Edge Port Module (EPORT)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

16-4

Freescale Semiconductor

16.4.2

EPORT Data Direction Register (EPDDR)

The EPORT data direction register (EPDDR) controls the direction of each one of the pins individually.

16.4.3

Edge Port Interrupt Enable Register (EPIER)

The EPORT interrupt enable register (EPIER) enables interrupt requests for each pin individually.

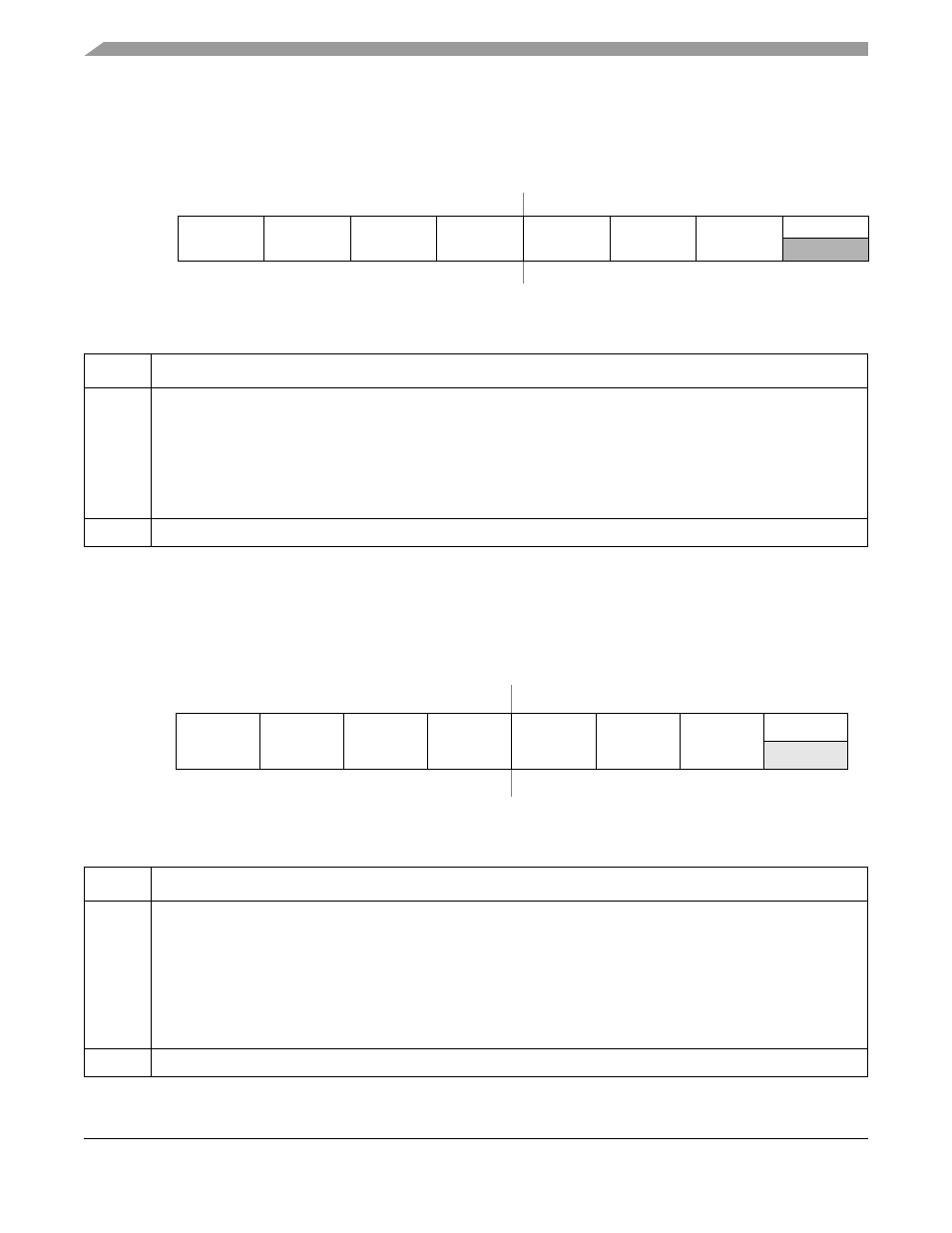

: 0x002 (EPDDR)

Access: Supervisor read/write

7

6

5

4

3

2

1

0

R

EPDD7

EPDD6

EPDD5

EPDD4

EPDD3

EPDD2

EPDD1

0

W

Reset

0

0

0

0

0

0

0

0

Figure 16-3. EPORT Data Direction Register (EPDDR)

Table 16-4. EPDDR Field Descriptions

Field

Description

7–2

EPDDn

Setting any bit in the EPDDR configures the corresponding pin as an output. Clearing any bit in EPDDR configures

the corresponding pin as an input. Pin direction is independent of the level/edge detection configuration. Reset clears

EPDD7–EPDD1.

To use an EPORT pin as an external interrupt request source, its corresponding bit in EPDDR must be clear.

Software can generate interrupt requests by programming the EPORT data register when the EPDDR selects output.

0 Corresponding EPORT pin configured as input

1 Corresponding EPORT pin configured as output

1-0

Reserved, must be cleared.

IPSBAR

Offset:

0x13_0003 (EPIER)

Access: User read/write

7

6

5

4

3

2

1

0

R

EPIE7

EPIE6

EPIE5

EPIE4

EPIE3

EPIE2

EPIE1

0

W

Reset:

0

0

0

0

0

0

0

0

Figure 16-4. EPORT Port Interrupt Enable Register (EPIER)

Table 16-5. EPIER Field Descriptions

Field

Description

7–1

EPIEn

Edge port interrupt enable bits enable EPORT interrupt requests. If a bit in EPIER is set, EPORT generates an

interrupt request when:

• The corresponding bit in the EPORT flag register (EPFR) is set or later becomes set.

• The corresponding pin level is low and the pin is configured for level-sensitive operation.

Clearing a bit in EPIER negates any interrupt request from the corresponding EPORT pin. Reset clears

EPIE7–EPIE1.

0 Interrupt requests from corresponding EPORT pin disabled

1 Interrupt requests from corresponding EPORT pin enabled

0

Reserved, must be cleared.