1 mcf52211 family configurations, Mcf52211 family configurations -2 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 18

Overview

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

1-2

Freescale Semiconductor

1.1

MCF52211 Family Configurations

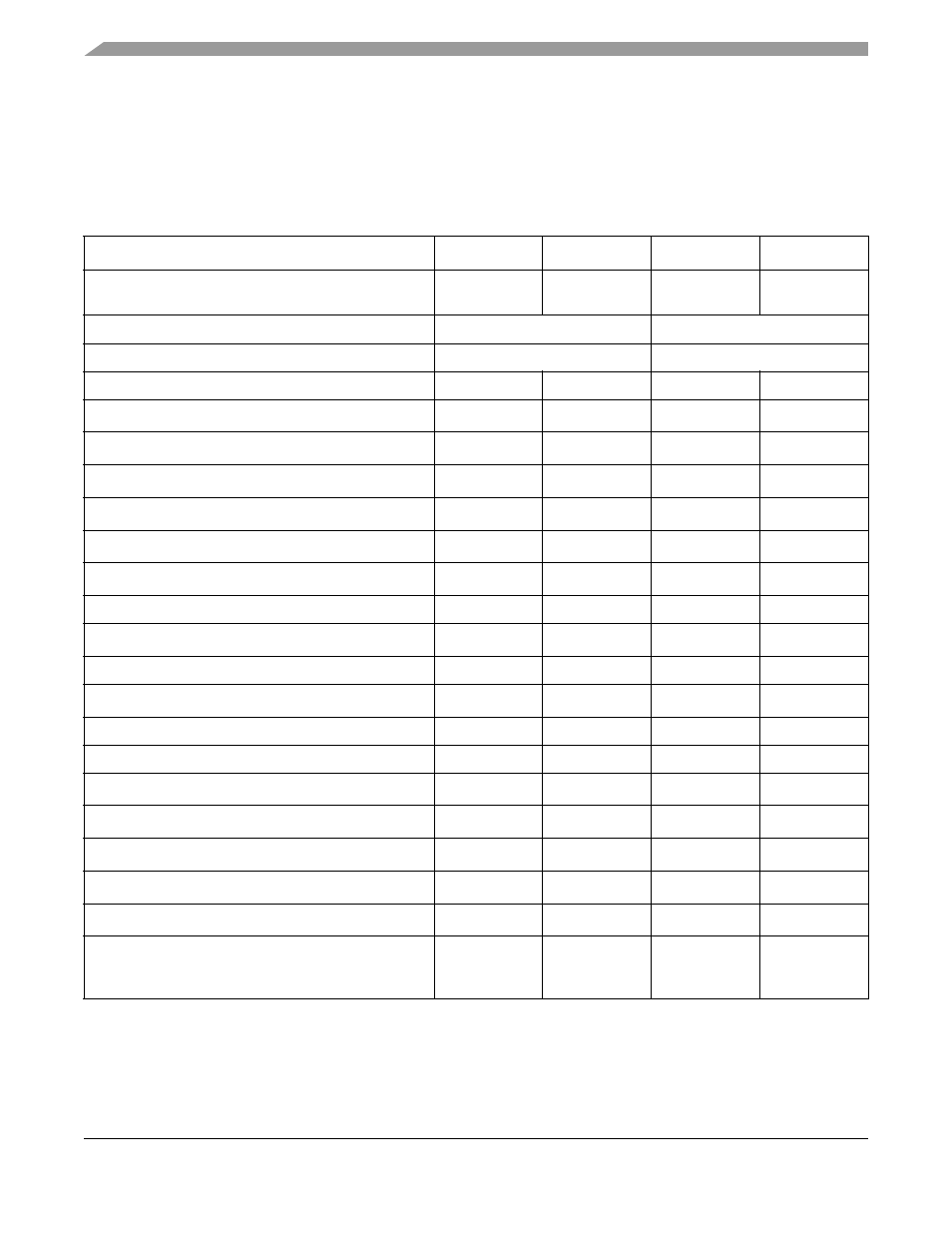

Table 1-1. MCF52211 Family Configurations

Module

52210

52211

52212

52213

Version 2 ColdFire Core with MAC (Multiply-Accumulate

Unit)

•

•

•

•

System Clock

66, 80 MHz

50 MHz

Performance (Dhrystone 2.1 MIPS)

up to 76

up to 46

Flash / Static RAM (SRAM)

64/16 Kbytes

128/16 Kbytes

64/8 Kbytes

128/8 Kbytes

Interrupt Controller (INTC)

•

•

•

•

Fast Analog-to-Digital Converter (ADC)

•

•

•

•

USB On-The-Go (USB OTG)

•

•

•

•

Four-channel Direct-Memory Access (DMA)

•

•

•

•

Software Watchdog Timer (WDT)

•

•

•

•

Secondary Watchdog Timer

•

•

•

•

Two-channel Periodic Interrupt Timer (PIT)

2

2

2

2

Four-Channel General Purpose Timer (GPT)

•

•

•

•

32-bit DMA Timers

4

4

4

4

QSPI

•

•

•

•

UART(s)

2

3

2

2

I

2

C

2

2

2

2

Eight/Four-channel 8/16-bit PWM Timer

•

•

•

•

General Purpose I/O Module (GPIO)

•

•

•

•

Chip Configuration and Reset Controller Module

•

•

•

•

Background Debug Mode (BDM)

•

•

•

•

JTAG - IEEE 1149.1 Test Access Port

1

1

The full debug/trace interface is available only on the 100-pin packages. A reduced debug interface is bonded on smaller

packages.

•

•

•

•

Package

64 LQFP/QFN

81 MAPBGA

64 LQFP/QFN

81 MAPBGA

100 LQFP

64 LQFP

64 LQFP