2 lvds connector pinout (j6) – Comtech EF Data SDM-2020 User Manual

Page 198

SDM-2020 Satellite Demodulator

Revision 4

ASI/LVDS Data Interface MN/SDM2020D.IOM

13–8

13.1.6

Connector Pinout Data

13.1.6.1

ASI Connector Pinout

The ASI interface is shown below:

J3, J4

Transmit Data Input, BNC female

J7

Receive Data Output, BNC female

13.1.6.2 LVDS

Connector Pinout (J6)

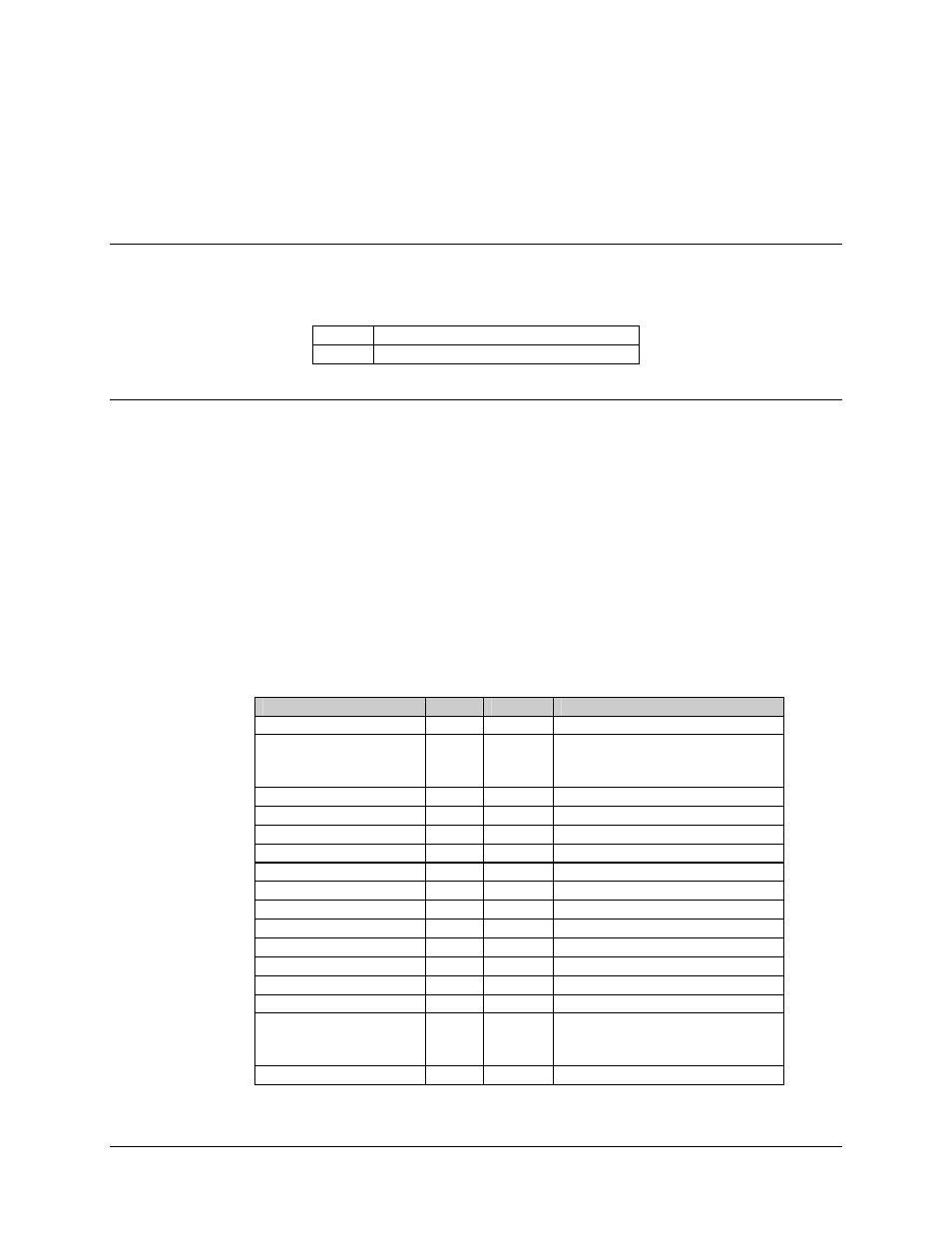

The LVDS connector (Table 13-4) is a 25-Pin D female type, with threaded jack nuts.

LVDS signal levels are as defined in EN 50083-9. The differential sense of all signal

pairs is a logic “1” when “A” is positive with respect to “B.” Some DBS applications

require an inverted data or clock polarity and control of the signal polarity (normal or

inverted) is provided.

Input / Output (I/O) of the interface is determined by a) whether it is plugged into a

modulator or demodulator and b) Loopback or Loop Thru programming.

Table 13-4. LVDS Connector Pinout (J6)

Signal Function/Name

Pin #

Type

Comment

Clock A

1

I / O

Mod / Demod

System Gnd / REFCLKB 2

O / Gnd

Mod / Demod,

Demod – GND only, no clock

available

Data 7 A(MSB/Serial)

3

I / O

Mod / Demod

Data 6 A

4

I / O

Mod / Demod

Data 5 A

5

I / O

Mod / Demod

Data 4 A

6

I / O

Mod / Demod

Data 3 A

7

I / O

Mod / Demod

Data 2 A

8

I / O

Mod / Demod

Data 1 A

9

I / O

Mod / Demod

Data 0 A

10

I / O

Mod / Demod

DVALID A

11

I / O

Mod / Demod

SYNC A

12

I / O

Mod / Demod

Cable Shield

13

I / O

Mod / Demod

Clock B

14

I / O

Mod / Demod

System Gnd / REFCLKA

15

O / Gnd

Mod / Demod

Demod – GND 0nly, no clock

available

Data 7 B (MSB/Serial)

16

I / O

Mod / Demod