Altera LVDS SERDES Transmitter / Receiver User Manual

Page 71

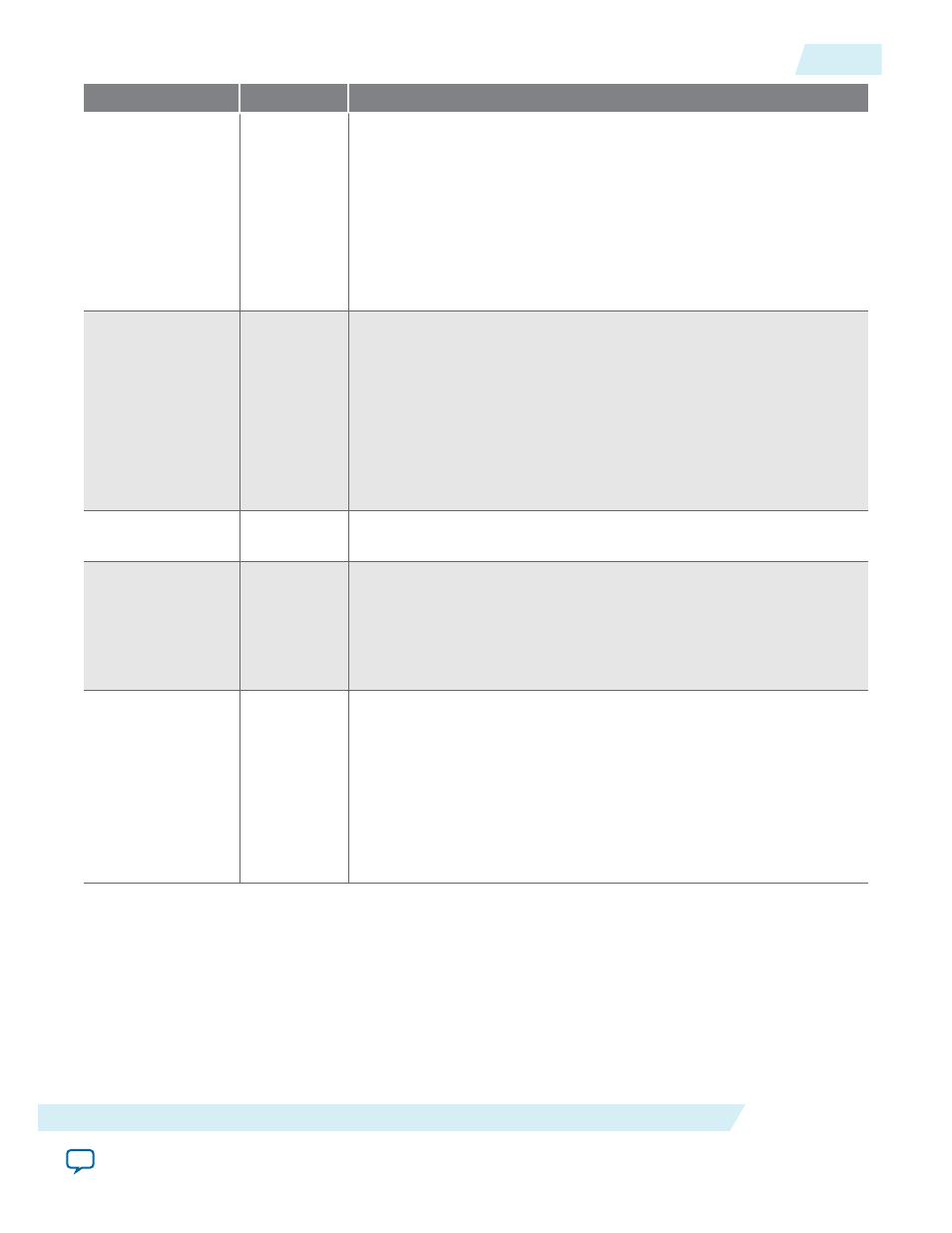

Date

Version

Changes

June 2011

v.8.0

• Reorganized the document format.

• Added "Source-Synchronous Timing Analysis and Timing

Constraints" section.

• Added "Generating Clock Signals for LVDS Interface" section.

• Updated the timing diagram in the "Receiver Skew Margin and

Transmitter Channel-to-Channel Skew" section.

• Updated "Parameter Settings" chapter.

• Added "Using Clear Box Generator" section.

August 2010

v.7.0

• Updated "DPA PLL Calibration in Stratix III and Stratix IV E

Devices" section.

• Added Verilog HDL prototypes.

• Added VHDL LIBRARY-USE declaration.

• Added VHDL Component Declarations.

• Added new ports and parameters.

• Added new parameter settings.

• Removed Design Examples for this release.

November 2009

v6.1

Added "Arria II GX and Stratix V LVDS Package Skew Compensation

Report Panel".

September 2009

v6.0

• Added "Device Support".

• Updated "Specifications" section to include "Ports and Parameters

in ALTLVDS_RX Megafunction" and "Ports and Parameters in

ALTLVDS_TX Megafunction".

• Added "Specifications".

March 2009

v5.0

• Updated Table 4, and Table 12.

• Added DPA Misalignment Issue, Figure 3, and "DPA PLL Calibra‐

tion", Figure 20 and Figure 21.

• Added Table 11 ALTLVDS Receiver DPA settings 3 option (page 7)

and Table 19 Configuration Settings for Design Example 4 (LVDS

Receiver).

• Added description about "Design Example 4: Stratix III ALTLVDS

Receiver with DPA PLL Calibration.

UG-MF9504

2014.12.15

Document Revision History

71

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation