Altlvds_rx parameter settings – Altera LVDS SERDES Transmitter / Receiver User Manual

Page 16

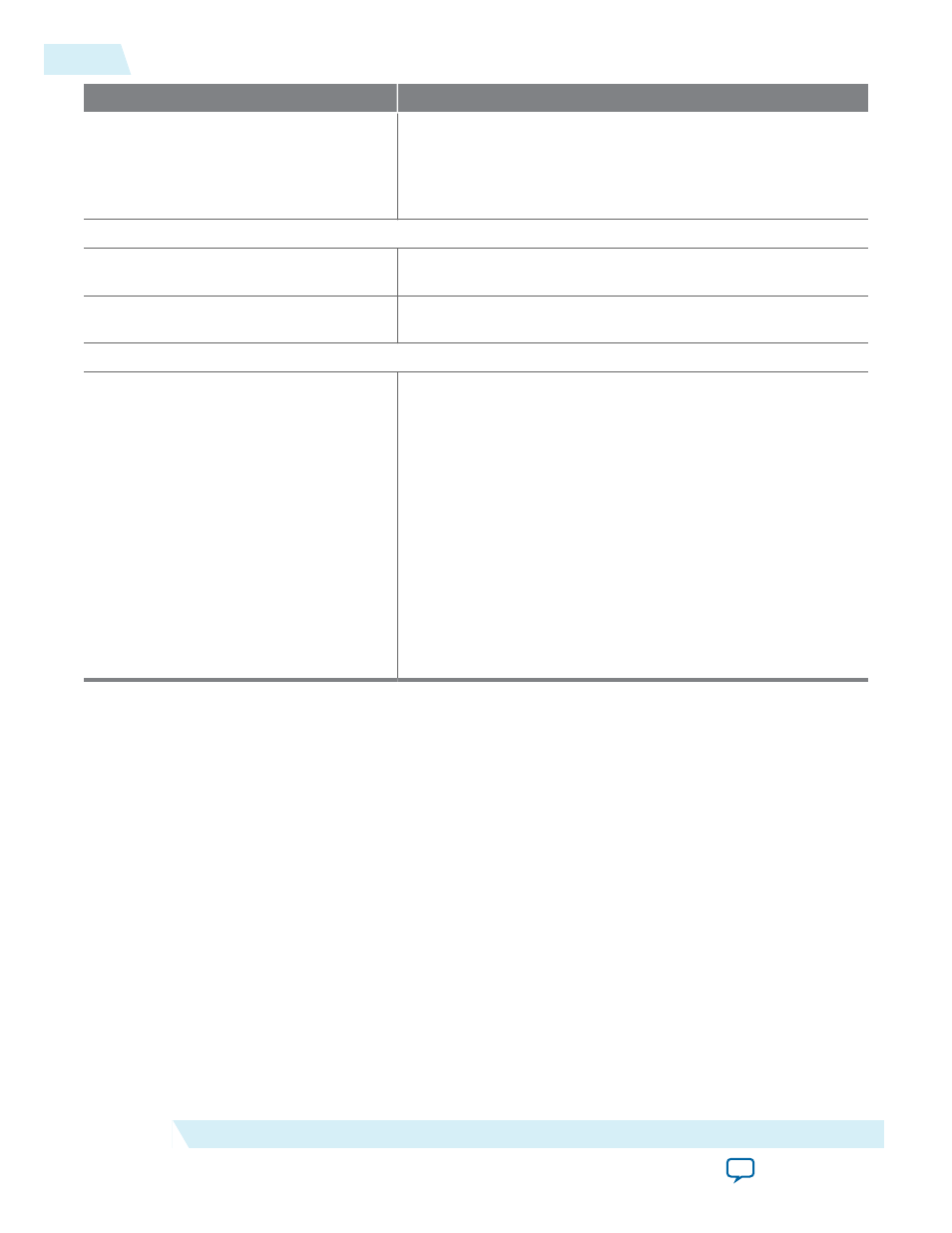

Option

Description

What is the clock resource used for 'tx_

coreclock'?

Specifies the clock resource type fed to the

tx_coreclock

signal. Allowed values are Auto selection (the Compiler

determines the type), Global clock, and Regional clock.

The default value is Auto selection.

Simulation Model (page 6)

Simulation Libraries

Specifies the libraries needed for functional simulation by

third-party tools.

Generate netlist

Specifies whether to turn on the option to generate synthesis

area and timing estimation netlist.

Summary (page 7)

Summary

Specifies the types of files to be generated. A gray checkmark

indicates a file that is automatically generated; a green

checkmark indicates an optional file.

Choose from the following types of files:

• AHDL Include file (

• VHDL component declaration file (

• Quartus II symbol file (

• Instantiation template file (

• Verilog HDL block box file (

• Pin Planner File (

If you turn on the Generate netlist option, the file for that

netlist is also available (

Related Information

•

ALTLVDS_RX Parameter Settings

On the General page (page 3) of the parameter editor, depending on the device you selected, you can

configure the following options:

• Implement the SERDES circuitry in LEs (logic cells) or dedicated SERDES

• Use internal PLL or external PLL

• Use DPA mode or non-DPA mode

The selections you make on the General page determine the features available on the remaining pages of

the parameter editor.

The following table lists the parameter settings for the LVDS receiver IP core.

16

ALTLVDS_RX Parameter Settings

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide