Altera LVDS SERDES Transmitter / Receiver User Manual

Page 41

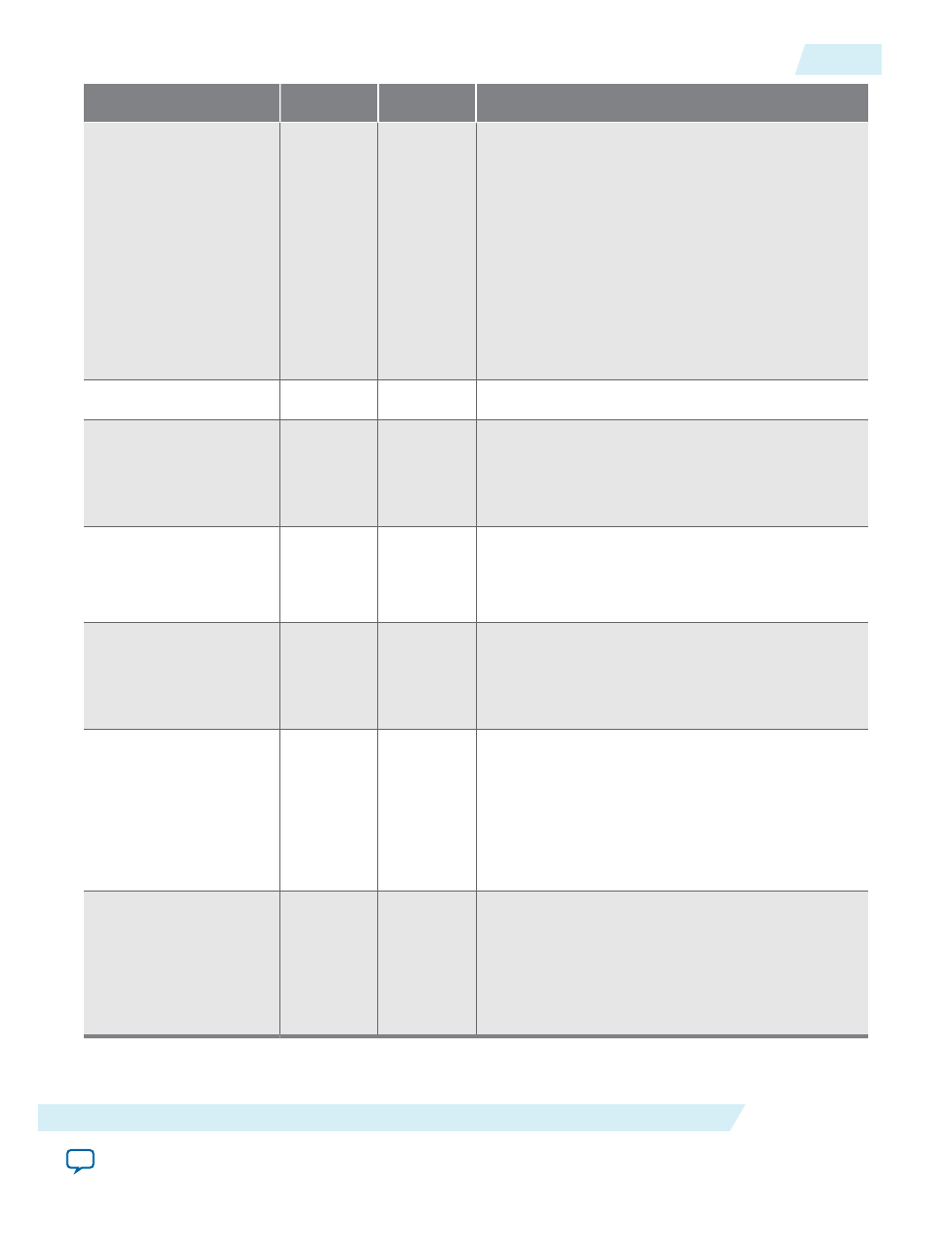

Port Name

Direction

Width (Bit)

Description

tx_inclock

Input

1

Reference clock input for the transmitter PLL.

The parameter editor automatically selects the

appropriate PLL multiplication factor based on the

data rate and reference clock frequency selection.

When using Stratix II devices in external PLL mode,

connect the

tx_inclock

port to the

sclkout0

or

sclkout1

port. When using Cyclone and Cyclone II

devices in external PLL mode, connect the

tx_

inclock

port to other clocks.

Refer to the respective device handbook for

supported input clock frequency ranges.

tx_pll_enable

Input

1

Enables control for the LVDS PLL.

tx_syncclock

Input

1

Slow clock input port.

In the Quartus II software version 8.0 or later, the

tx_syncclock

port is necessary for even deseriali‐

zation factors in external PLL mode.

tx_coreclock

Output

1

Output clock used to feed non-peripheral logic.

FPGA fabric-transmitter interface clock. The

parallel transmitter data generated in the FPGA

fabric must be clocked with this clock.

tx_locked

Output

1

Provides the LVDS PLL status.

This port stays high when the PLL is locked to the

input reference clock, and stays low when the PLL

fails to lock.

tx_out[]

Output

n

Serialized LVDS data output port of n channels

wide.

tx_out[(n-1)..0]

drives parallel data from

tx_

in[(J * n)-1 ..0]

where J is the serialization

factor and n is the number of channels.

tx_out[0]

drives data from

tx_in[(J-1)..0]

.

tx_out[1]

drives data from the next J number of bits on

tx_in

.

tx_outclock

Output

1

External reference clock.

The frequency of this clock is programmable to be

the same as the data rate (up to 717 MHz), half the

data rate, or one-fourth the data rate. The phase

offset of this clock, with respect to the serial data, is

programmable in increments of 45°.

UG-MF9504

2014.12.15

ALTLVDS_TX Ports

41

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation