Altera LVDS SERDES Transmitter / Receiver User Manual

Page 43

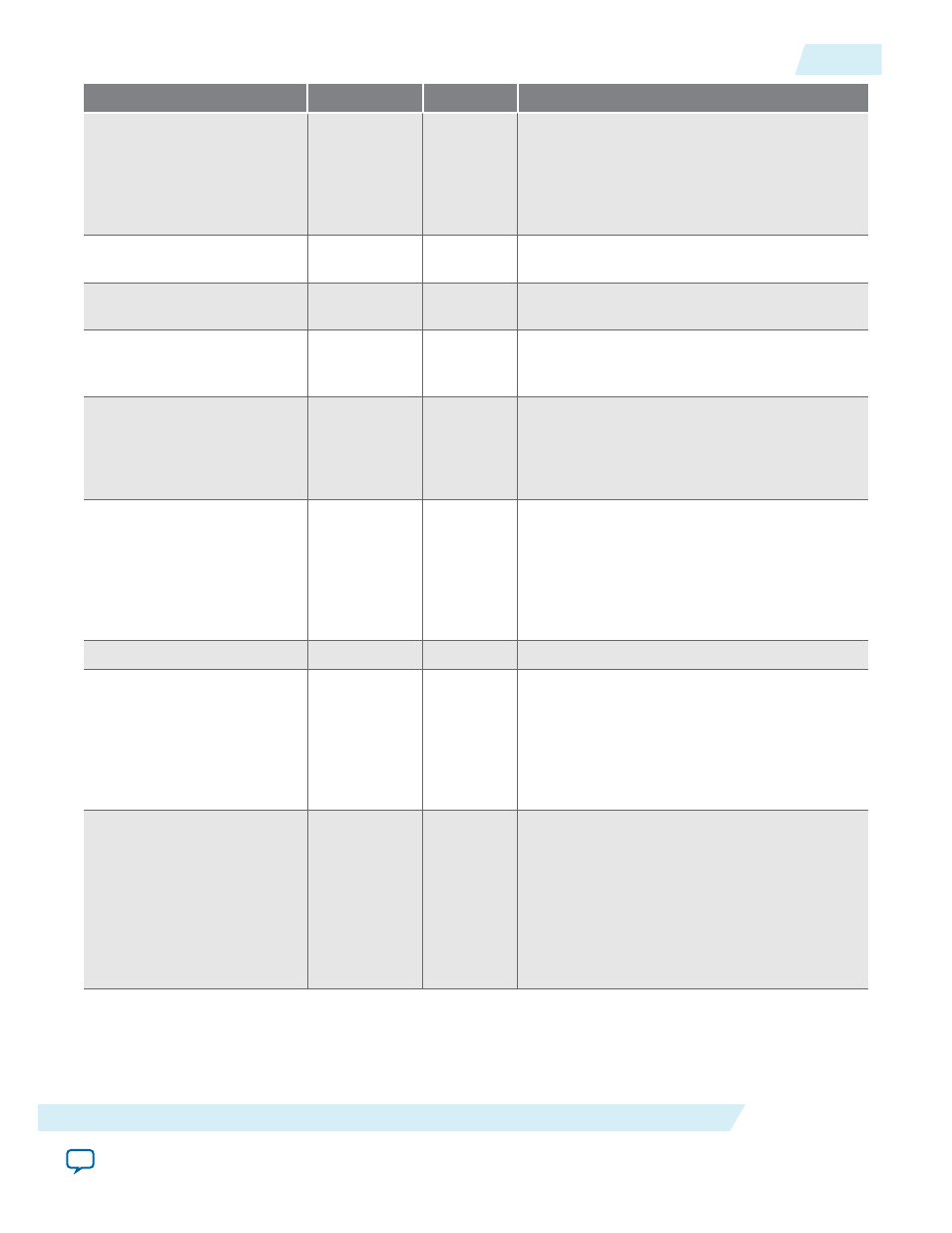

Port Name

Direction

Width (Bit)

Description

rx_data_align_reset

Input

1

Resets the byte alignment circuitry. Use the

rx_data_align_reset

input port when you

need to reset the PLL during device operation

and when you need to re-establish the word

alignment. This port is available when

implement_in_les

parameter is set to ON.

rx_data_reset

Input

n

Asynchronous reset for all channels,

excluding the PLL.

rx_deskew

Input

1

Specifies whether to activate calibration

mode.

rx_dpa_lock_reset

Input

n

Forces the

rx_dpa_locked

port to low and

forces the lock counter to start counting

again.

rx_dpll_enable

Input

n

Enables the data path that flows through the

DPA circuit. This port is available only when

DPA mode is enabled. This port is supported

in Arria GX, HardCopy II, Stratix II, and

Stratix II GX devices only.

rx_dpll_hold

Input

n

Prevents the DPA circuitry from switching to

a new phase. When low, the DPA tracks any

dynamic phase variations between the clock

and data. When high, the DPA holds the last

locked phase and does not track any dynamic

phase variations between the clock and data.

This port is not available in non-DPA mode.

rx_dpll_reset

Input

n

Asynchronous reset for all channels.

rx_enable

Input

1

Enables external PLL usage. When the

rx_

enable

port is specified, it must connect to

the enable0 or enable1 port of a PLL IP core

instance configured in LVDS mode. However,

the

enable0

,

enable1

ports and the Set up

PLL in LVDS mode option are available for

Stratix II devices only.

rx_fifo_reset

Input

n

Asynchronous reset to the FIFO between the

DPA and the data realignment circuits. The

synchronizer block must be reset after a DPA

loses lock condition and the data checker

shows corrupted received data. The minimum

pulse width requirement for this reset is one

parallel clock cycle. This signal resets the

FIFO block. Only available when DPA mode

is enabled.

UG-MF9504

2014.12.15

ALTLVDS_RX Ports

43

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation