Altera LVDS SERDES Transmitter / Receiver User Manual

Page 68

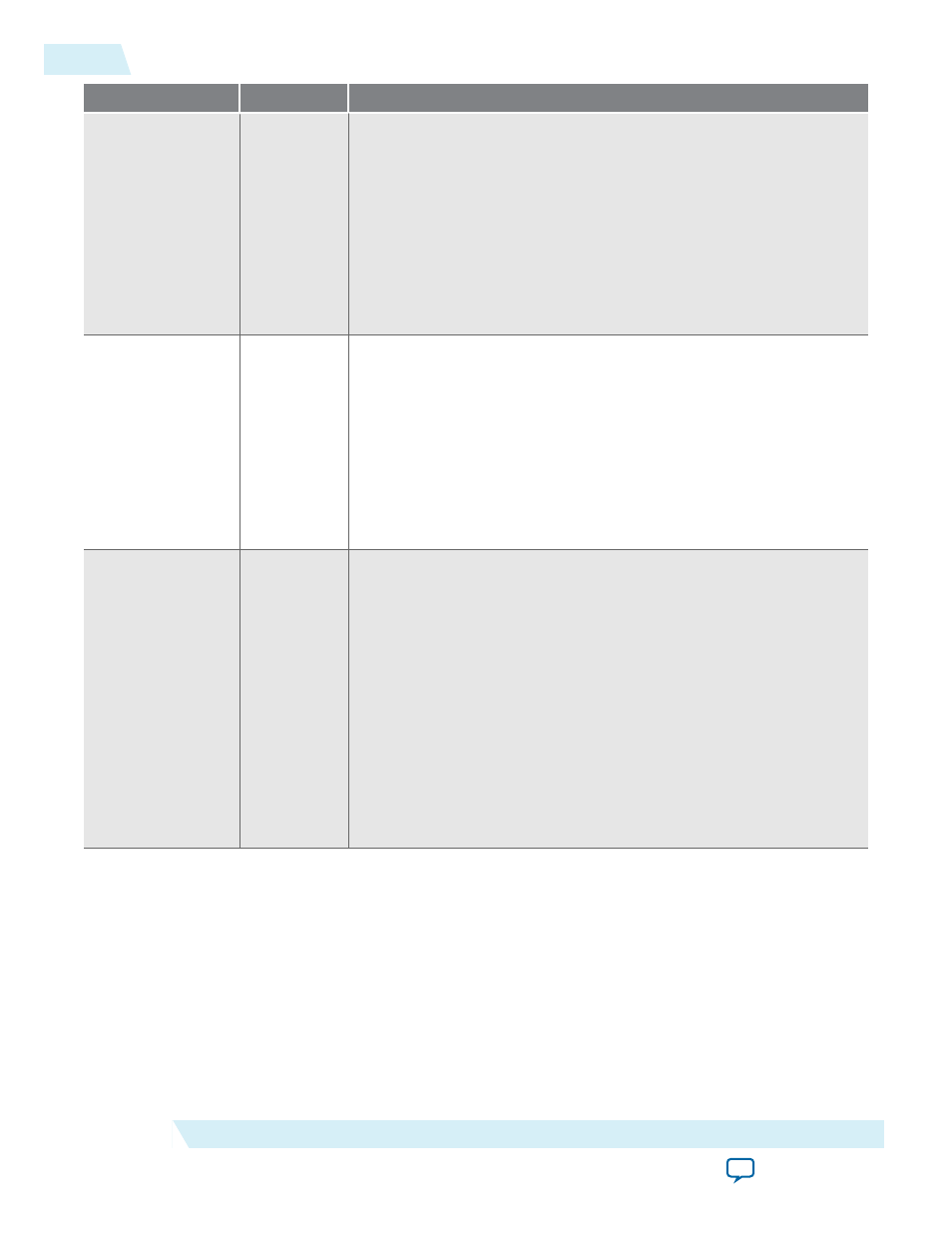

Date

Version

Changes

November 2014

2014.11.17 • Restructured and updated sections that describe the external PLL

mode and the relevant ALTPLL IP core parameters.

• Added recommendations about getting the correct ALTPLL

phase shift and duty cycle values for the external PLL mode.

• Clarified that the

rx_syncclock

is automatically created by the

Quartus II software only when it is required.

• Updated the ALTLVDS_RX ports list to clarify that the

rx_cda_

reset

port is not supported in Arria V and Cyclone V devices. In

these devices, use the

rx_channel_data_align

signal instead.

June 2014

2014.06.30 • Replaced MegaWizard Plug-In Manager information with IP

Catalog.

• Added standard information about upgrading IP cores.

• Added standard installation and licensing information.

• Removed outdated device support level information. IP core device

support is now available in IP Catalog and parameter editor.

• Updated a statement about valid data availability for

rx_channel_

data_align

signal in the topic about ALTLVDS_RX parameter

settings.

November 2013

2013.11.08 Updated the following parameters:

•

outclock_alignment

: clarify that this parameter is only used by

the RTL simulation model and has no affect on how the Fitter sets

the PLL parameters.

•

outclock_phase_shift

: clarified that this parameter is used to set

the phase shift parameters used by the PLL.

Updated the following parameters:

•

inclock_data_alignment

: clarified that this parameter is only

used by the RTL simulation model and has no affect on how the

Fitter sets the PLL parameters.

•

inclock_phase_shift

: clarified that this parameter is used to set

the phase shift parameters used by the PLL.

68

Document Revision History

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide