Altera LVDS SERDES Transmitter / Receiver User Manual

Page 30

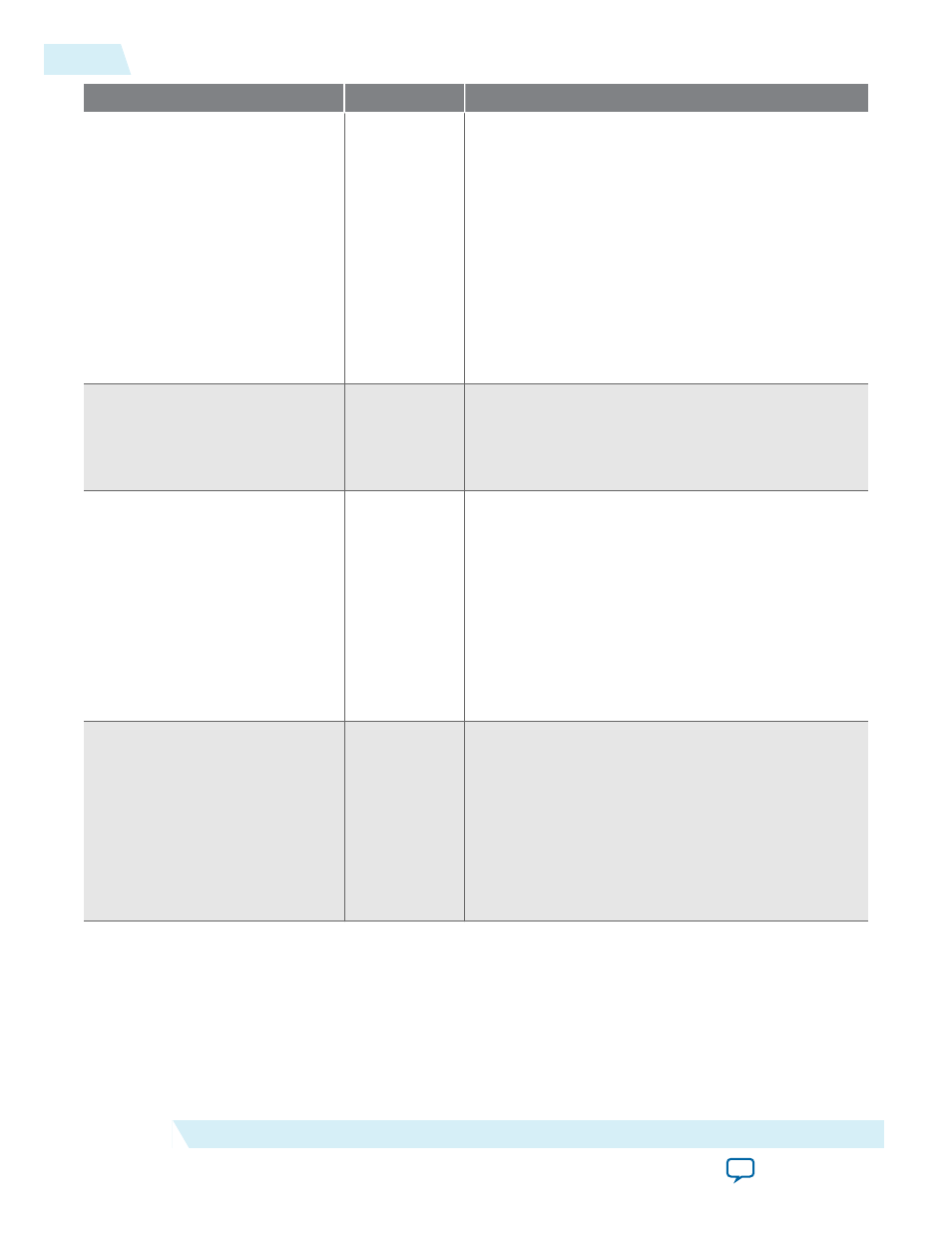

Parameter

Type

Description

outclock_duty_cycle

Integer

Specifies the external clock timing constraints. A

value of 50 is not supported in the outclock_duty_

cycle parameter when the following is true:

•

DESERIALIZATION_FACTOR

value is

5

,

7

, or

9

.

•

OUTCLOCK_DIVIDE_BY

value is equal to the value of

DESERIALIZATION_FACTOR

.

•

OUTCLOCK_MULTIPLY_BY

value is

2

.

This is always true for Cyclone II, Cyclone III,

Cyclone IV devices, and true for Arria V, Arria V GZ,

Stratix II, Stratix III, Stratix IV, and Stratix V devices

when the

implement_in_les

parameter value is set

to

ON

.

outclock_multiply_by

Integer

Specifies the multiplication factor. The values are

1

and

2

. If omitted, the default value is

1

.

Only available for Cyclone, Cyclone II, Stratix, Stratix

GX, and Stratix II devices.

outclock_phase_shift

Integer

This parameter is used to set the phase shift

parameters used by the PLL.

Specifies the phase shift of the output clock relative to

the input clock. Phase shifts of 0.0, 0.25, 0.5, or 0.75

times the input period (0, 90, or 270°) are

implemented precisely. The allowed range for the

phase shift is between 0 ps and 1 input clock period.

If the phase shift is outside this range, the compiler

adjusts it to fall within this range. For other phase

shifts, the compiler chooses the closest allowed value.

If omitted, the default value is

0

.

outclock_resource

String

Specifies the clock resource type to use with the

tx_

coreclock

port. The values are

AUTO

,

REGIONAL

CLOCK

, and

GLOBAL CLOCK

. If omitted, the default

value is

AUTO

.

Only available for Arria GX, Arria II GX, Arria II GZ,

Arria V, Arria V GZ, Cyclone, Cyclone II, Cyclone

III, Cyclone IV, HardCopy II, HardCopy III,

HardCopy IV, Stratix, Stratix GX, Stratix II, Stratix II

GX, Stratix III, Stratix IV, and Stratix V devices.

30

Command Line Interface Parameters

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide