Altera LVDS SERDES Transmitter / Receiver User Manual

Page 14

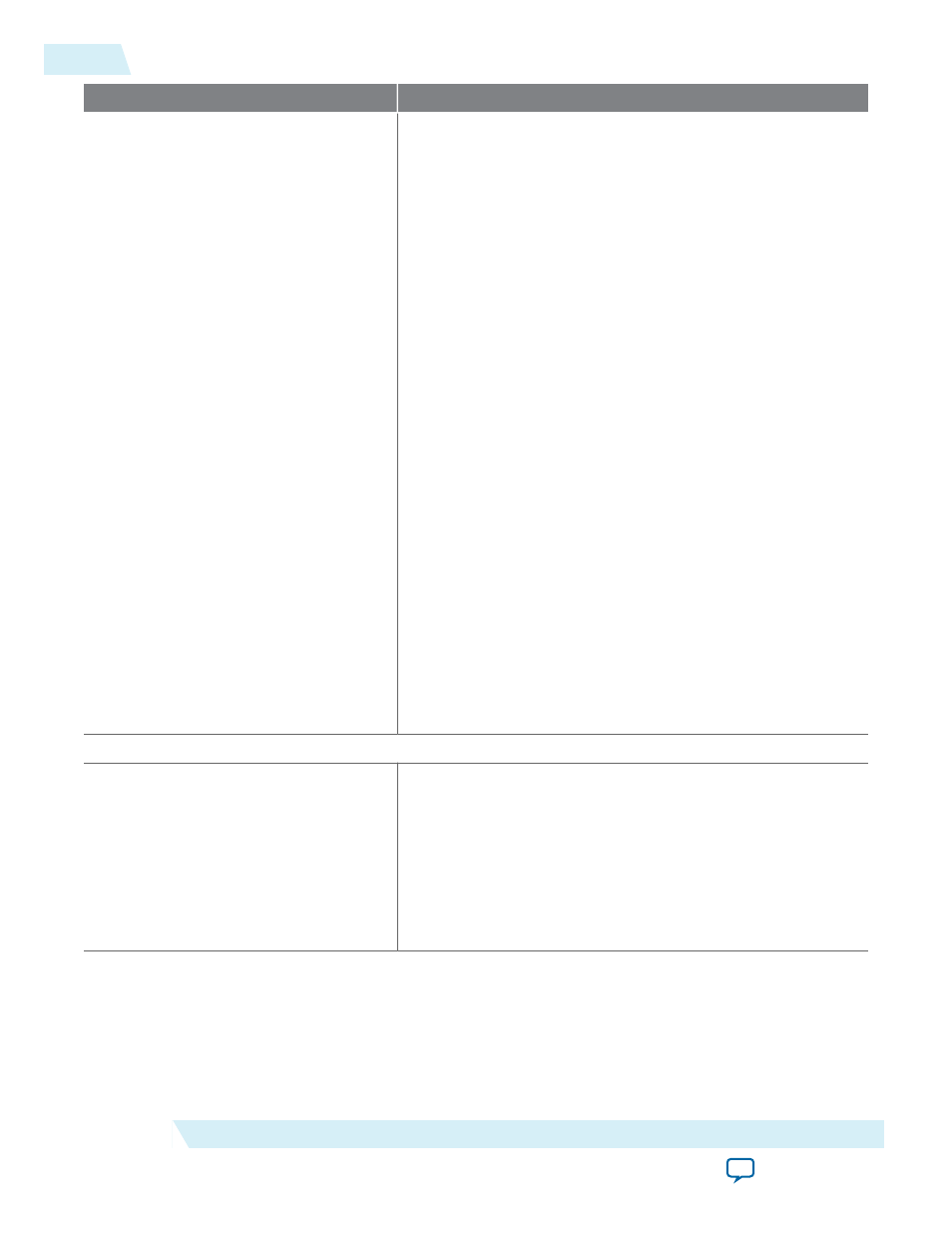

Option

Description

Register 'tx_in' input port using

Turn on this option to specify whether input registers are

clocked by the

tx_inclock

signal or

tx_coreclock

signal.

When the PLLs are shared, connect the

tx_inclock

signal to

the same reference clock as the receiver function. For example,

if the

tx_inclock

signal is connected to a 500-MHz input

reference clock, and the parallel data rate is not 500 MHz,

register the parallel data using the

tx_coreclock

signal that

runs at the output serial data rate divided by the deserialization

factor. This frequency matches the parallel data rate from the

FPGA core.

If you turn off this option, a warning message appears that

directs you to pre-register the inputs in the logic that feeds the

transmitter. When you use the Cyclone series with the

ALTLVDS_TX and ALTLVDS_RX IP cores, the interface

always sends the most significant bit (MSB) of your parallel

data first.

When you use the ALTLVDS_TX IP core, you might get setup

timing violations when you use the

tx_inclock

signal to

register the data that feeds the SERDES blocks. The ALTLVDS_

TX IP core gives you the choice to register the

tx_in[]

data

with either the

tx_inclock

or

tx_coreclock

signal. The

default setting is

tx_coreclock

. Using the

tx_coreclock

signal to register the data before it feeds the SERDES is the

better choice, because it has the optimal phase position to

register the data with respect to the high-speed clock that drives

the SERDES. Your setup timing violations are eliminated when

you use the

tx_coreclock

signal instead of the

tx_inclock

signal to register the data in the ALTLVDS_TX IP core.

Additionally, you get better timing margins when you use the

tx_coreclock

signal instead of the

tx_inclock

signal, even if

you do not have timing violations.

Transmitter Settings (page 5)

Use 'tx_outclock' output port

The

tx_outclock

signal is associated with the serial transmit

data stream.

Every

tx_outclock

signal goes through the shift register logic,

excluding the following parameter configurations:

• When the

outclock_divide_by

signal equals to 1, or

• When the

outclock_divide_by

signal equals to

deserial-

ization_factor

signal (for odd factors only) and the

outclock_duty_cycle

signal is 50.

14

ALTLVDS_TX Parameter Settings

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide