Altera LVDS SERDES Transmitter / Receiver User Manual

Page 28

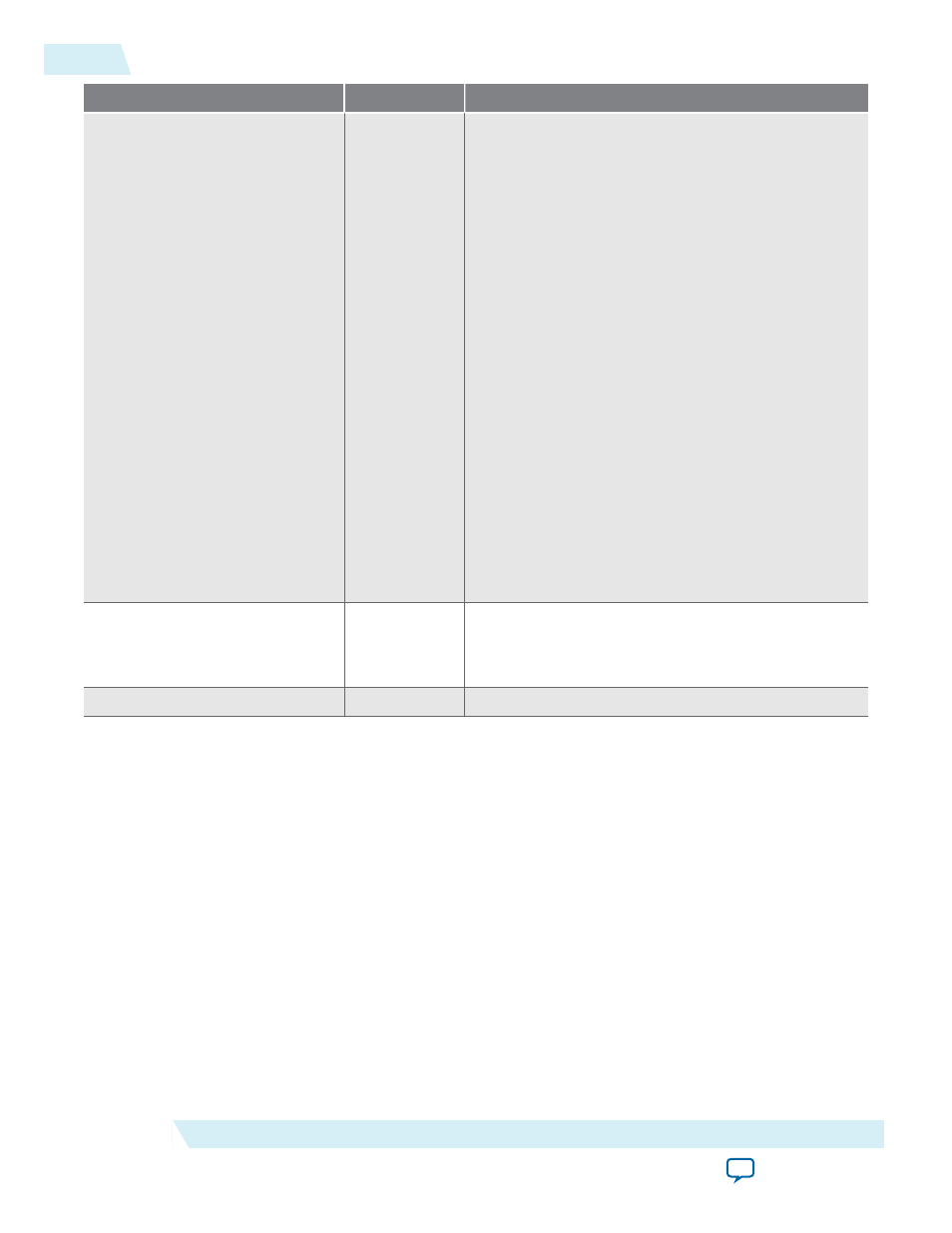

Parameter

Type

Description

inclock_data_alignment

String

Specifies the phase alignment of the

tx_in[]

and

tx_

inclock

input ports in terms of the

tx_inclock

frequency. The clock phase alignment for the

inclock_data_alignment

parameter specifies the

positive phase shift needed for the clock for

alignment with the data.

The following are the parameter values and its values

in degrees (°):

•

EDGE_ALIGNED: 0°

•

45_DEGREES: 45°

•

90_DEGREES: 90°

•

135_DEGREES: 135°

•

CENTER_ALIGNED: 180°

•

225_DEGREES: 225°

•

270_DEGREES: 270°

•

315_DEGREES: 315°

If omitted, the default value is

EDGE_ALIGNED

.

Available for Arria GX, Arria II GX, Arria II GZ,

Arria V, Arria V GZ, Cyclone, Cyclone II, Cyclone

III, Cyclone IV, HardCopy II, HardCopy III,

HardCopy IV, Stratix, Stratix GX, Stratix II, Stratix II

GX, Stratix III, Stratix IV, and Stratix V devices.

inclock_period

Integer

Specifies the input clock either by frequency (MHz in

the parameter editor) or period (ps in HDL code).

This parameter is required when the external PLL

option is not used.

number_of_channels

Integer

Specifies the number of LVDS channels.

28

Command Line Interface Parameters

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide