Altera LVDS SERDES Transmitter / Receiver User Manual

Page 15

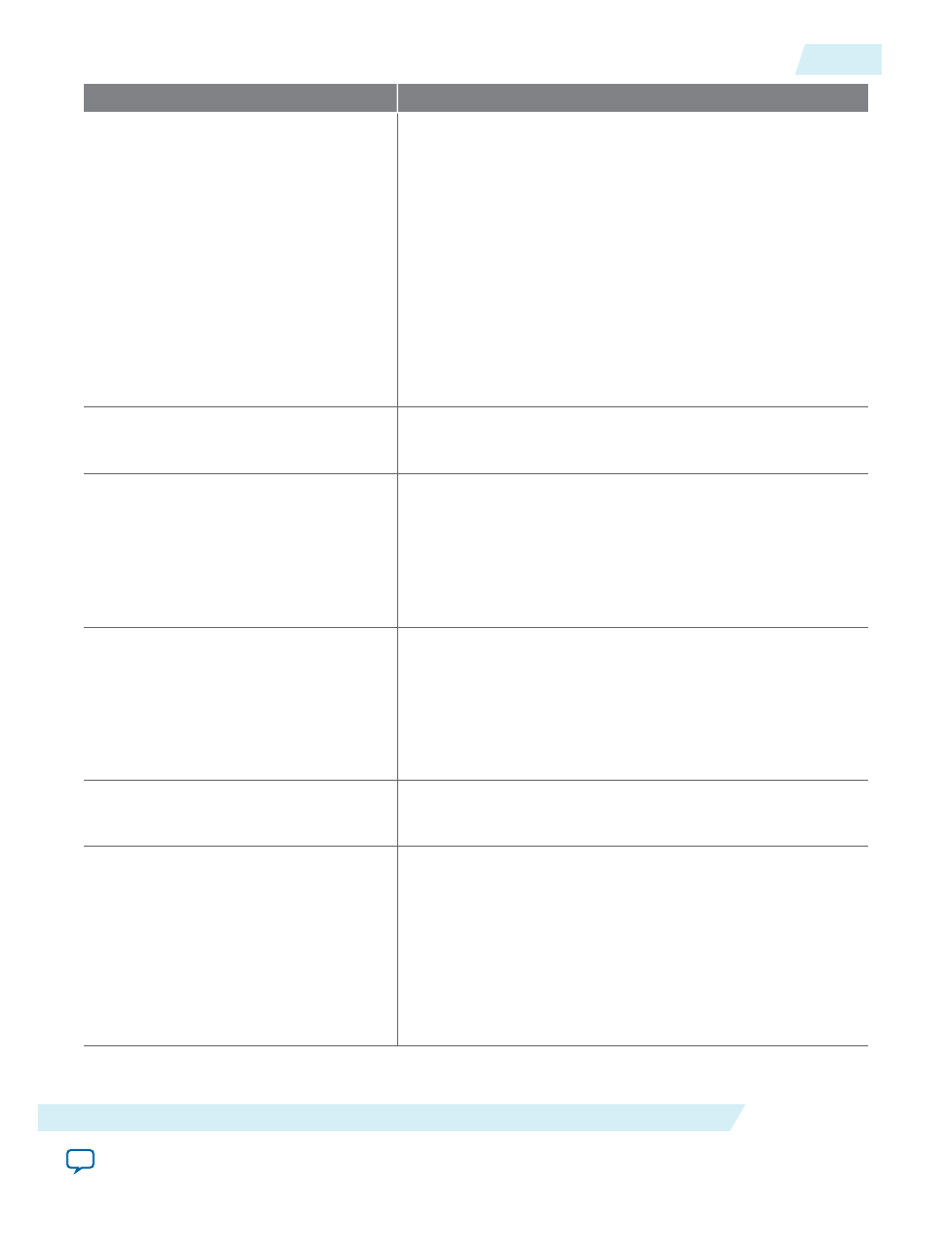

Option

Description

What is the outclock divide factor (B)? Specifies the frequency of the

tx_outclock

signal as the

transmitter output data rate divided by the outclock divide

factor (B). For the legal values, refer to the relevant device

handbook.

For a SERDES factor of 5 and 9, the outclock divide factors

available are 1, 5, and 9. The divide factor of 2 is not available.

For Cyclone II devices and later, when the

implement_in_les

parameter is

ON

, the

outclock_duty_cycle

of 50 is not

supported in the following parameter configurations:

• deserialization_factor signal is 5, 7, or 9

•

outclock_divide_by

signal equals to

deserialization_

factor

•

outclock_multiply_by

is 2

Specify phase alignment of 'tx_

outclock' with respect to 'tx_out'

Specifies the phase alignment of

tx_outclock

signal with

respect to the

tx_out

signal. This option is available only if you

use the

tx_outclock

signal.

What is the phase alignment of 'tx_

outclock' with respect to 'tx_out'?

The available values are 0.00, 22.50, 45.00, 67.50, 90.00,

112.50, 135.00, 157.50, 180.00, 202.50, 225.00, 247.50, 270.00,

292.50, 315.00, and 337.50.

The values for this option are device dependent.

This option is available only when you implement the SERDES

in logic cells and uses the

tx_outclock

signal.

What is the outclock duty cycle?

The default value is 50.

The

outclock_duty_cycle

of 50 is not supported when:

•

deserialization_factor

signal is 5, 7, or 9

•

outclock_divide_by

signal equals to

deserialization_

factor

•

outclock_multiply_by

is 2

Use 'tx_locked' output port

Allows you to monitor the lock status of the PLL. The status of

the lock port is identical for the transmitter and receiver when

the IP core uses shared PLLs.

Use 'tx_coreclock' output port

Turn on this option to show the core clock frequency during

simulation. Enables the transmitter core clock signal to the

registers of all the logic that feeds the LVDS transmitter

function. If any other clock feeds the transmit function, your

design must implement the clock domain transfer circuitry.

You must add a false path constraint from the

slow_clock

signal to the

fast_clock

signal in the ALTLVDS_TX IP core

whenever the faster

core_clock

signal implementation is used

for odd deserialization factors.

UG-MF9504

2014.12.15

ALTLVDS_TX Parameter Settings

15

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation