Altera LVDS SERDES Transmitter / Receiver User Manual

Page 61

Port Name

Constraint Type

Option

Description

GUI Setting

SDC command

Rise, Fall, Both

-clock fall

-clock rises

Specifies the clock's rising

and falling edges or the

duty cycle of the clock.

rx_in

set_input_delay

Delay

-

Specifies the data to clock

skew in ns.

Target

[get_ports

{

name>}

]

Specifies the data input

port name connected to

rx_in

.

Related Information

Arria II GX, Arria V, Arria V GZ, Cyclone V, and Stratix V LVDS Package Skew

Compensation Report Panel

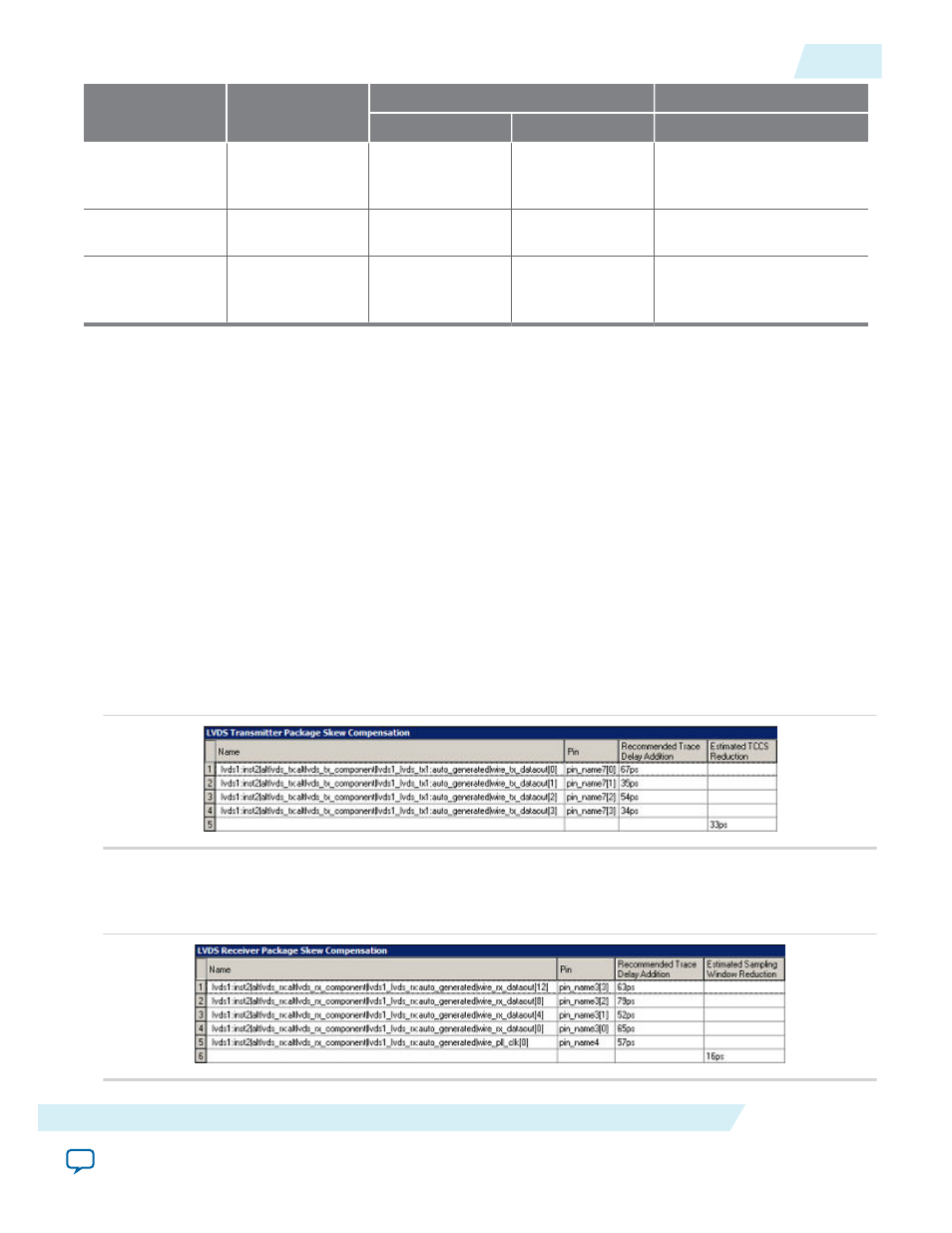

This section describes the LVDS package skew compensation report panel for the transmitter and non-

DPA receiver of the Arria II GX, Arria V, Arria V GZ, Cyclone V, and Stratix V device families.

The report panel contains details about the package trace delay compensation needed between the LVDS

pins on the device to meet your timing budget. You can find the report panel in the Quartus II Fitter

report under Resource Section. The report panel is called LVDS Receiver Package Skew Compensation,

and LVDS Transmitter Package Skew Compensation for the LVDS receiver and LVDS transmitter

respectively. The report panel is triggered in the Quartus II software when your design uses a non-DPA

receiver, and with an input data rate higher than 840 Mbps.

The following figure shows the LVDS Transmitter Package Skew Compensation report panel.

Figure 12: LVDS Transmitter Package Skew Compensation

The following figure shows the LVDS Receiver Package Skew Compensation report panel.

Figure 13: LVDS Receiver Package Skew Compensation

UG-MF9504

2014.12.15

Arria II GX, Arria V, Arria V GZ, Cyclone V, and Stratix V LVDS Package Skew

Compensation Report Panel

61

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation