Dedicated serdes, Serdes in les – Altera LVDS SERDES Transmitter / Receiver User Manual

Page 54

Dedicated SERDES

The ALTLVDS_TX and ALTLVDS_RX IP cores implemented in a dedicated SERDES and using the DPA

mode are characterized and guaranteed to function correctly within the LVDS system. Refer to the

respective device handbook for details about whether dedicated SERDES and DPA are supported for the

device family. The Quartus II compiler automatically ensures the associated delay chain settings are set

correctly for the data path at the LVDS transmitter/receiver that uses the source-synchronous compensa‐

tion mode of PLL operation.

You can optionally add false path constraints to the asynchronous input and output ports to avoid

unconstrained path warnings. For non-DPA mode, you can optionally constrain the synchronous input

ports to improve the accuracy of the receiver skew margin analysis.

Note: The TimeQuest Timing Analyzer automatically adds the required multicycle path, false path, and

clock uncertainty constraints to analyze timing for the dedicated SERDES if you add

derive_pll_clocks

to your Synopsys Design Constraints (.sdc) file.

SERDES in LEs

For receiver designs that are using the SERDES in LEs, you must ensure proper timing constraints for the

TimeQuest timing analyzer tool in the Quartus II software to indicate whether the SERDES captures the

data as expected or otherwise.

For dedicated SERDES and SERDES in LEs, you can set the timing constraints using the following

methods:

• Setting timing constraints using the TimeQuest Timing Analyzer GUI

• Setting timing constraints manually in the .sdc.

Receiver Skew Margin and Transmitter Channel-to-Channel Skew

Changes in system environment, such as temperature, media (cable, connector, or PCB), and loading,

affect the receiver's setup and hold times; internal skew affects the sampling ability of the receiver.

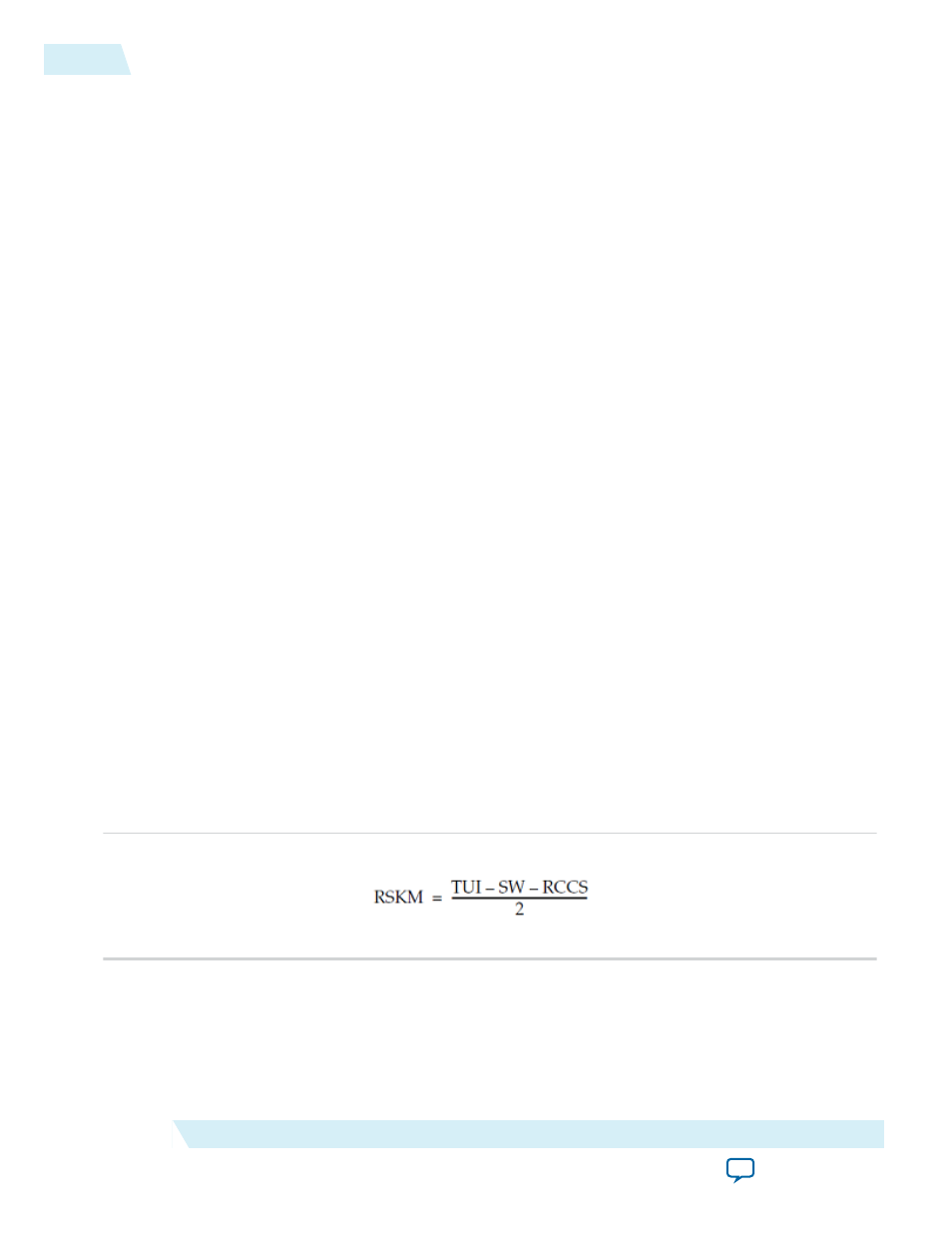

In non-DPA mode, use receiver skew margin (RKSM), receiver channel-to-channel skew (RCCS), and

sampling window (SW) specifications to analyze the timing for high-speed source-synchronous differen‐

tial signals in the receiver data path. The following equation shows the relationship between RSKM,

RCCS, and SW.

Figure 10: RSKM

54

Dedicated SERDES

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide