Altera LVDS SERDES Transmitter / Receiver User Manual

Page 19

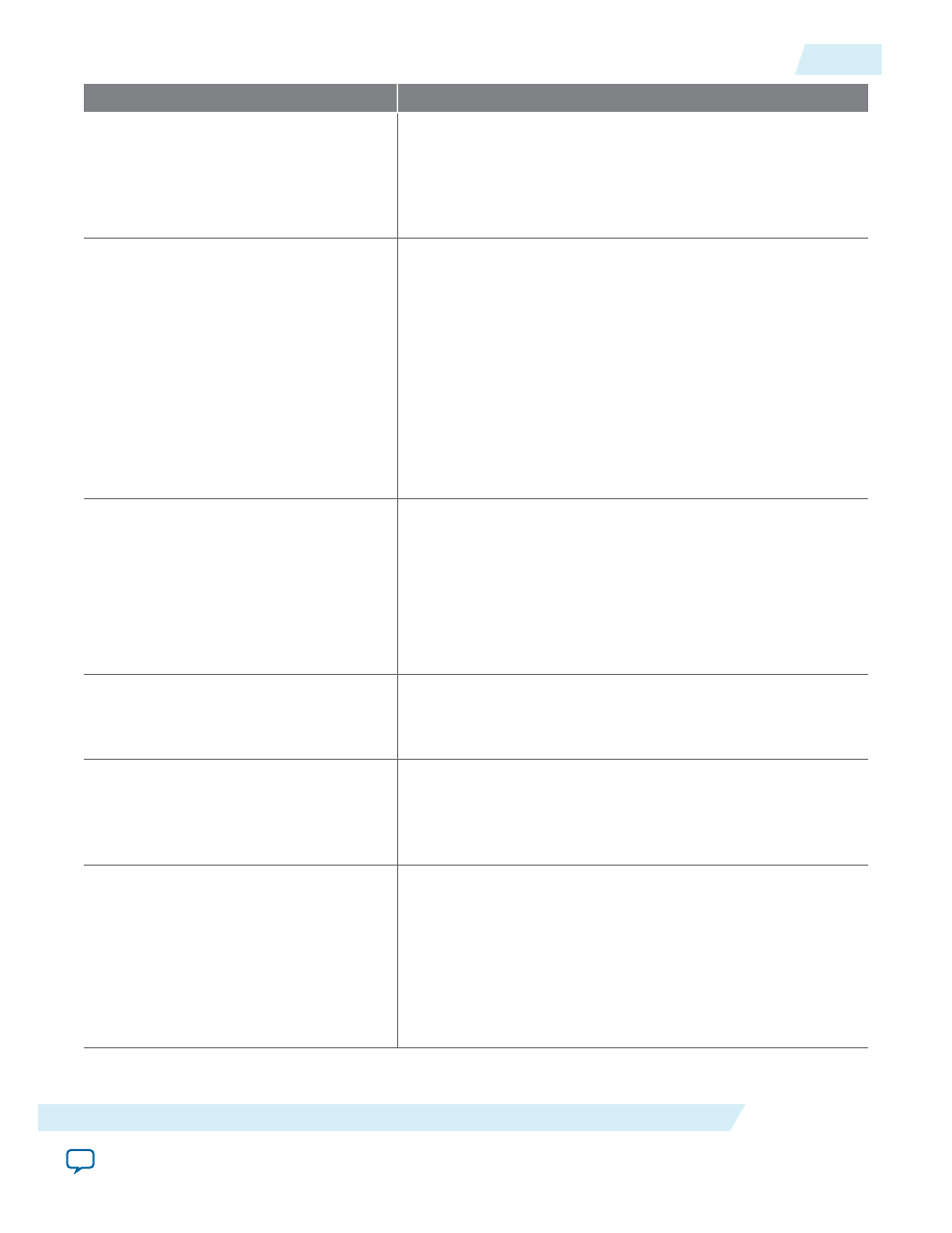

Option

Description

Use shared PLL(s) for receivers and

transmitters

When you turn on this option, your LVDS receivers and

transmitters can share the same PLL.

Turn on this option when the LVDS receivers and transmitters

use the same input clock frequency, deserialization factor, and

data rates.

Use 'pll_areset' input port

Turn on this option to control the asynchronous reset port of

the PLL that the IP core uses with this function.

When other ALTLVDS blocks share the PLL with the receiver

and use the

pll_areset

port, you must use this port in all IP

core instantiations and tie the signals together in the design file.

If you use the

pll_areset

port only in one IP core instance,

the PLLs are not shared, and a warning appears during

compilation.

The PLL must be reset to set the output clock phase relation‐

ships correctly when the PLL loses lock, or if the PLL input

reference clock is not stable when the device completes the

configuration process.

Use 'rx_pll_enable' input port

Turn on this option to control the enable port of the fast PLL

that the IP core uses with this function.

If the receiver shares the PLL with other ALTLVDS blocks, and

uses the

rx_pll_enable

port, you must use this port in all IP

core instances and tie the signal together in the design file. If

you use the

rx_pll_enable

port only in one IP core instance,

the PLLs are not shared and a warning appears during compila‐

tion.

Use 'rx_locked' output port

Turn on this option to monitor the lock status of the PLL. The

status of the lock port is identical for the transmitter and the

receiver when the IP cores use shared PLLs. In this case,

monitor the lock output from the receiver IP core.

What is the clock resource used for 'rx_

outclock'?

Specifies the clock resource type fed from the

rx_outclock

port. Legal values are Auto selection (the Compiler determines

the type), Global clock, and Regional clock.

The default value is Auto selection.

What is the phase alignment of 'rx_in'

with respect to 'rx_inclock'?

Determines the phase alignment of the data that the receiver

core receives with respect to the rx_inclock signal.

Available values are 0.00, 22.50, 45.00, 67.50, 90.00, 112.50,

135.00, 157.50, 180.00, 202.50, 225.00, 247.50, 270.00, 292.50,

315.00, and 337.50.

The values for this option are device dependent.

This option is only available if you turn off the DPA mode.

UG-MF9504

2014.12.15

ALTLVDS_RX Parameter Settings

19

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation