Altera LVDS SERDES Transmitter / Receiver User Manual

Page 18

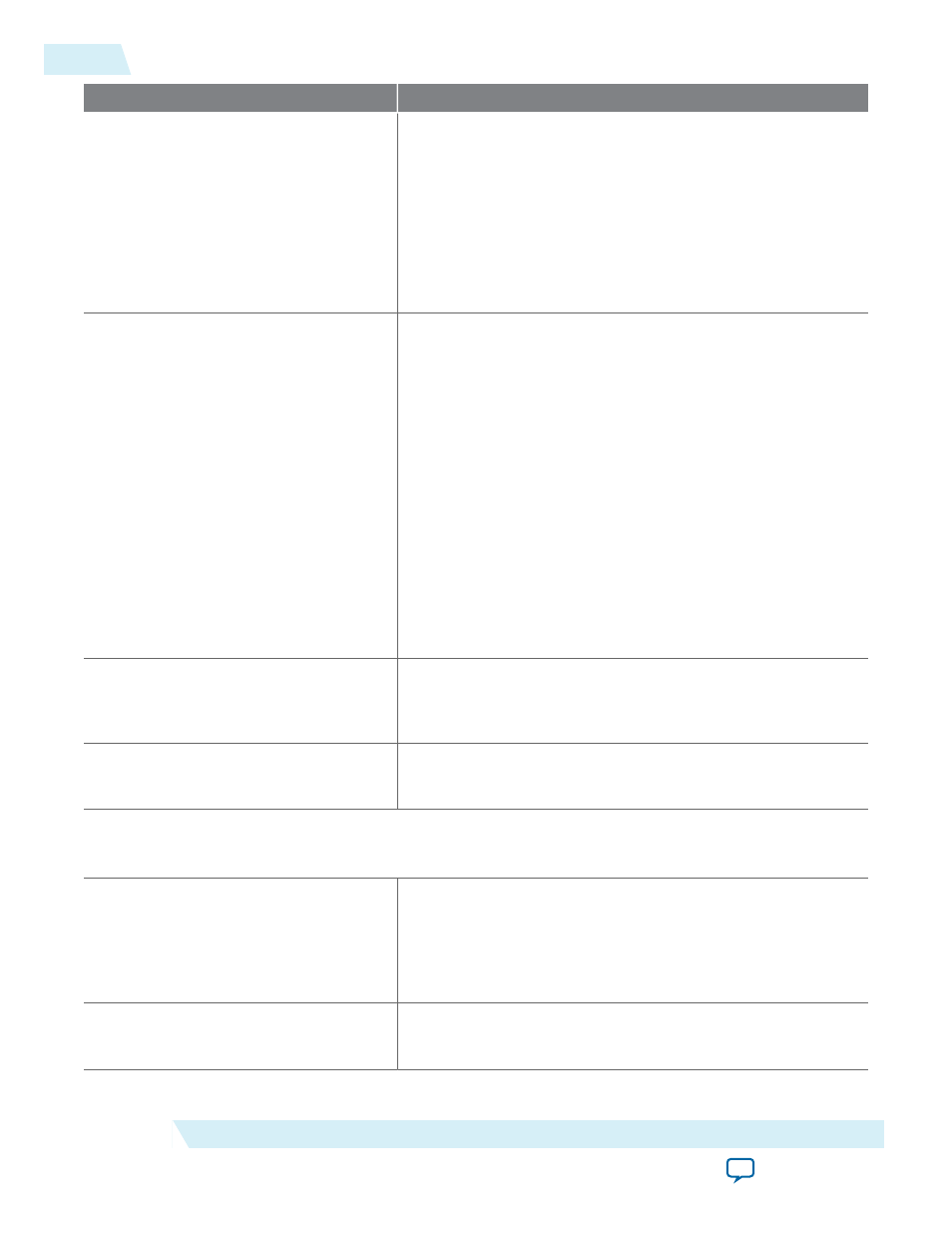

Option

Description

What is the deserialization factor?

Determines the number of serial input data bits that the

receiver deserializes and sends to the core on a single cycle. For

the valid deserialization factors for your device, refer to the

relevant device handbook.

For example, if the deserialization factor is 10 and the number

of input channels is 1, the receiver deserializes every 10 serial

bits into 10 bits of parallel data to send to the core. If the

deserialization factor is 10 and the number of channels is 44,

the port created is

rx_out[439..0]

.

Use External PLL

Turn on this option to use an external PLL to clock the

SERDES receiver. When you turn on this option, the options

on the Frequency/PLL settings page are disabled. You must

use a separate PLL to provide the clocking source and make the

necessary connections. You must ensure your circuit has the

correct input and functionality to generate an appropriate clock

frequency and is correctly connected to the LVDS receiver.

When you have a deserialization factor of two, the IP core

bypasses the SERDES and implements the SERDES function‐

ality in DDR registers. A deserialization factor of at least four is

required to use the external PLL option.

If you turn off this option, the IP core automatically

implements an internal PLL to clock the ALTLVDS_RX block.

For Stratix and Stratix GX devices, if you implement SERDES

for your LVDS transmitter using a dedicated SERDES block,

you do not have the option to use an external PLL.

Use 'rx_data_reset' input port

This option is enabled when you implement the LVDS in logic

cells. Turn on this option to add an input port to the IP core.

When the input port asserts, the IP core asynchronously resets

all the logic in the ALTLVDS_RX IP core excluding the PLL.

Is this interface constrained to the left,

or right banks?

Turn on this option if the LVDS interface is constrained to the

left or right IO banks. This option determines the PLL

compensation mode in Cyclone V devices.

Frequency/ PLL Settings (page 4)

The options on this page are available only when you are using internal PLL

What is the input data rate?

Specifies the data rate for the input channel of the receiver, in

Mbps.

For data rate ranges, refer to the specific Device Data Sheet

chapter in the respective device handbook. This value

determines the legal input clock rate values.

Specify input clock rate by

Specifies the clock frequency (

rx_inclock

) and the clock

period (

inclock_period

) for the internal PLL. The legal values

depend on the output data rate selected.

18

ALTLVDS_RX Parameter Settings

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide