Command line interface parameters – Altera LVDS SERDES Transmitter / Receiver User Manual

Page 26

Related Information

•

•

Command Line Interface Parameters

Expert users can choose to instantiate and parameterize the IP core through the command-line interface

using the clear box generator command. This method requires you to have command-line scripting

knowledge.

The following table lists the parameters for the ALTLVDS_TX IP core.

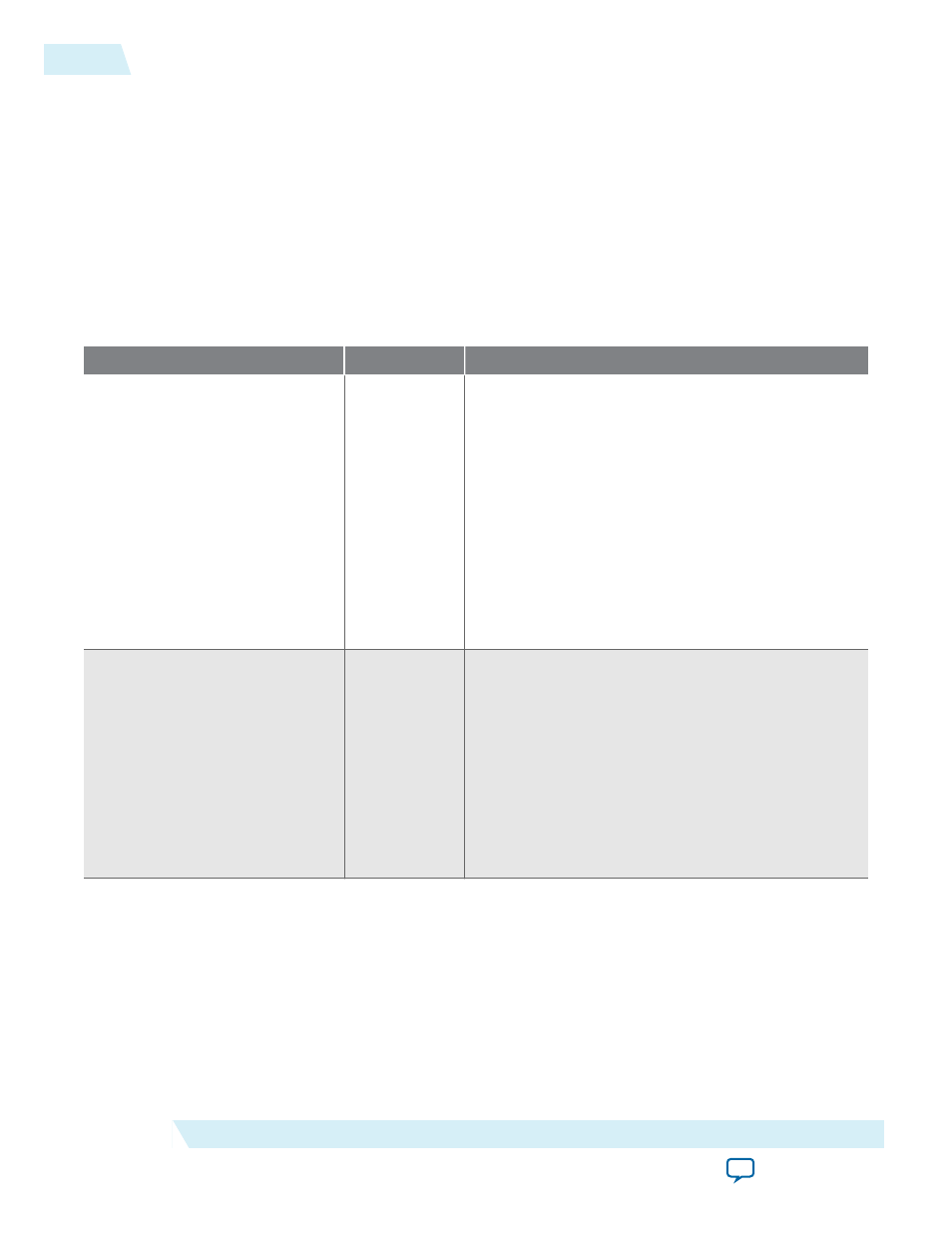

Table 7: ALTLVDS_TX Parameters

Parameter

Type

Description

common_rx_tx_pll

String

Specifies whether the compiler uses the same PLL for

both the LVDS receiver and the LVDS transmitter, or

multiple LVDS receivers, or multiple LVDS transmit‐

ters, or both. You can use common PLLs if the same

input clock source, same deserialization factor, same

pll_areset

source, and same data rates are used.

The values are

ON

and

OFF

. If omitted, the default

value is

ON

.

Only available for Arria GX, Arria II GX, Arria II GZ,

Arria V, Arria V GZ, Cyclone, Cyclone II, Cyclone

III, Cyclone IV, HardCopy II, HardCopy III,

HardCopy IV, Stratix, Stratix GX, Stratix II, Stratix II

GX, Stratix III, Stratix IV, and Stratix V devices.

coreclock_divide_by

Integer

Specifies the core clock output frequency to either be

core clock or core clock divided by 2. The value are

1

or

2

.

This parameter is only available when using odd

SERDES factors. When using a divide-by factor of 1,

fewer device resources are used, but you may not be

able to achieve timing at higher data rates.

Altera recommends using a divide-by factor of two

for higher data rates. This parameter is available for

the Cyclone series.

26

Command Line Interface Parameters

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide