Acx_serdes_sbus_if module – Achronix Speedster22i SerDes User Manual

Page 99

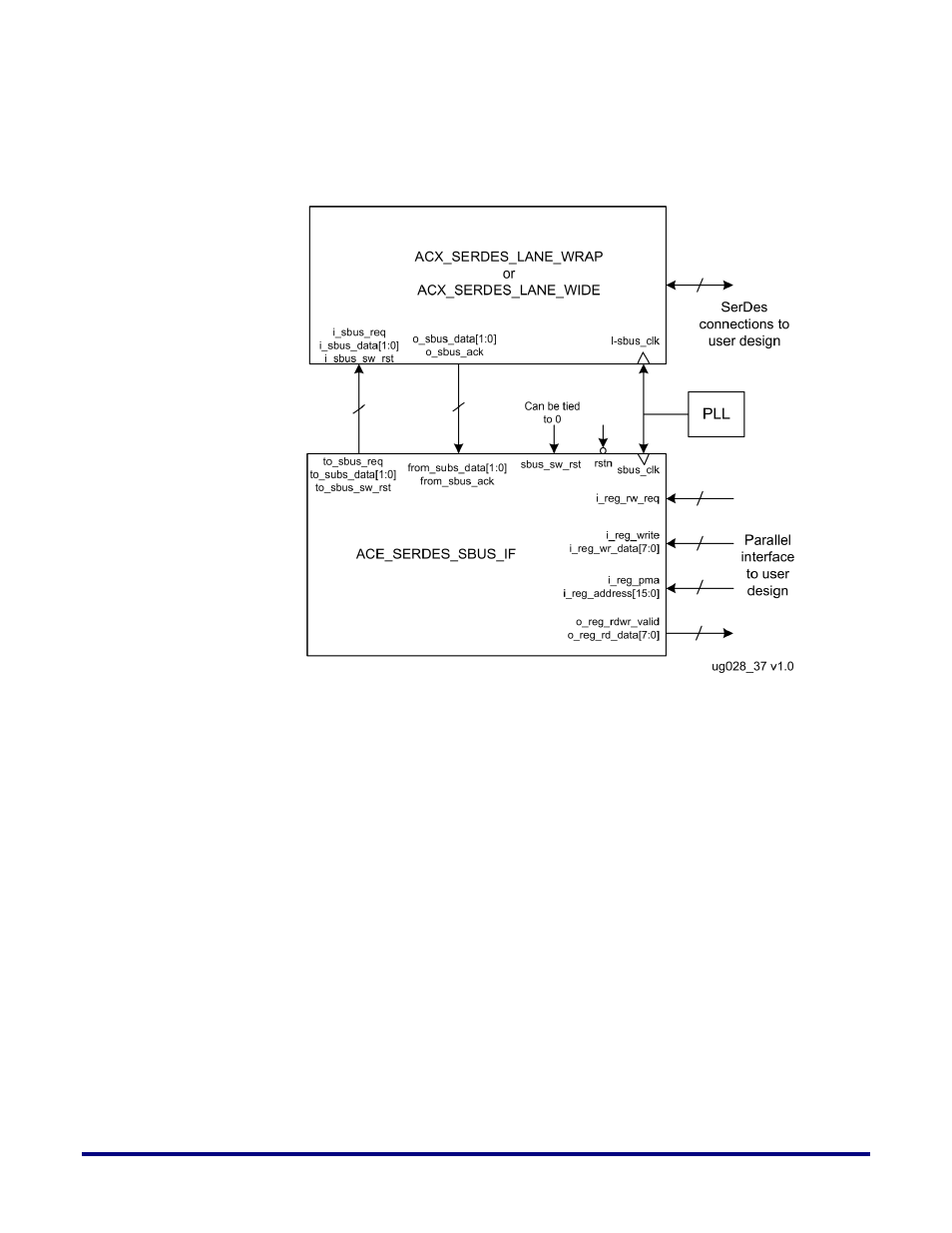

ACX_SERDES_SBUS_IF Module

The connection diagram for ACX_SERDES_SBUS_IF is shown in “Figure 44 Disabling PCS

Decoder (default ACE Setting)”.

Figure 44: Disabling PCS Decoder (default ACE Setting)

The code below presents the port definitions in ACX_SERDES_SBUS_IF module

module ACX_SERDES_SBUS_IF (

input sbus_clk,

input rstn,

input sbus_sw_rst, // active-high; may be tied low

// serdes connections

input [1:0] from_sbus_data,

input from_sbus_ack,

output [1:0] to_sbus_data,

output to_sbus_req,

output to_sbus_sw_rst,

// parallel interface

input i_reg_rw_req, // rising edge starts action

input i_reg_write, // request is 'write'

input i_reg_pma, // address is pma address

input [15:0] i_reg_address, // 16-bit pcs or pma address

input [7:0] i_reg_wr_data, // data for write

output [7:0] o_reg_rd_data, // data from read (latch when o_reg_rdwr_valid)

output reg o_reg_rdwr_valid // action finished (high for one cycle)

);

UG028, July 1, 2014

99