Table 9: latency across the pcs blocks – Achronix Speedster22i SerDes User Manual

Page 43

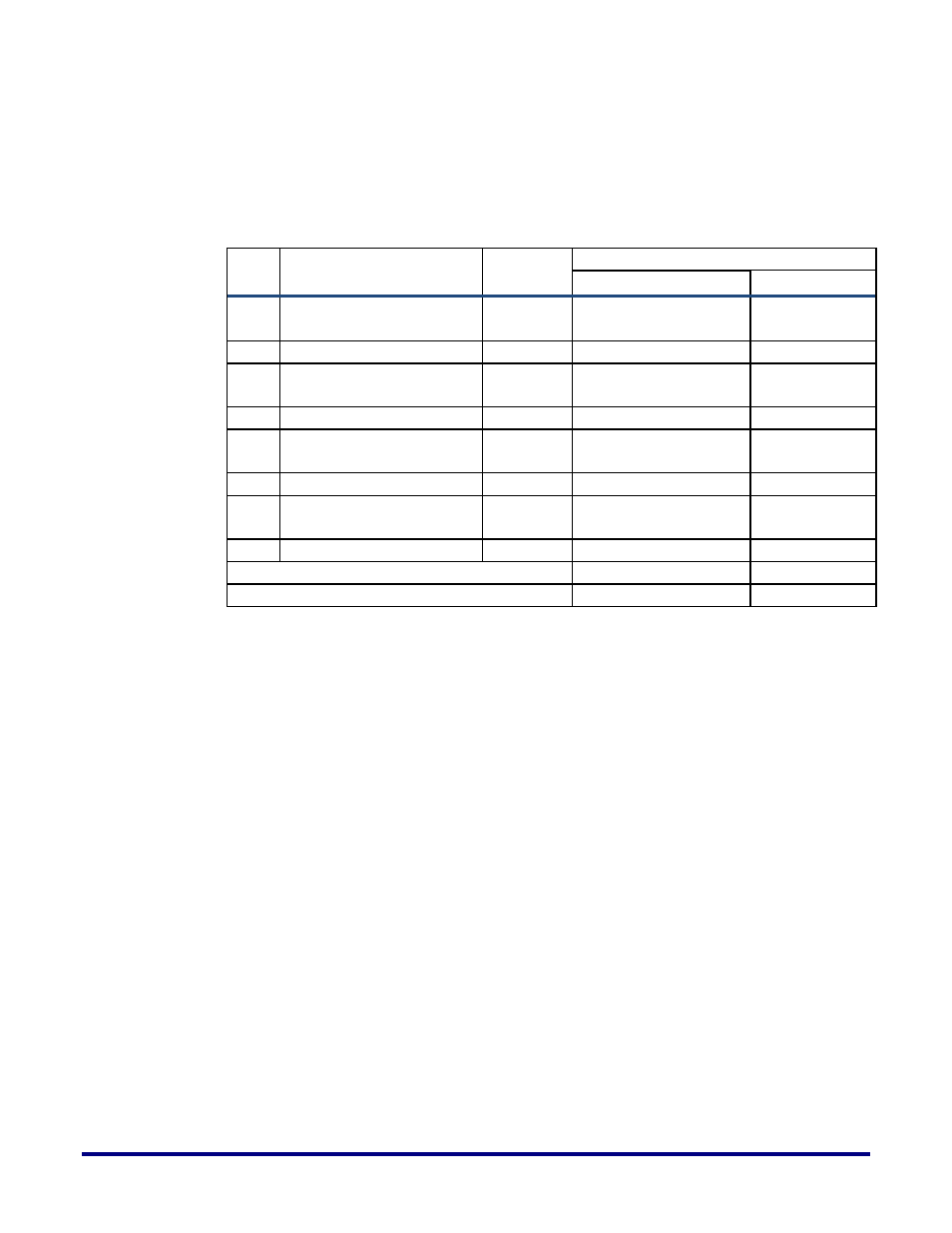

“Table 9: Latency across the PCS blocks” presents the latency experienced by datapath in

these two modes. The worst case latency is presented in in “Figure 20 Worst-case latency

across PMA and PCS”

Table 9: Latency across the PCS blocks

#

PCS Module

Data Path

Latency experienced by datapath

PCS Enabled

PCS Bypassed

1.

Polarity bit reversal

symbol swap 0

Transmit

0

Not applicable

2.

8b/10b Encoder

Transmit

2

Not applicable

3.

Polarity bit reversal

symbol swap 1

Receive

0

Not applicable

4.

8b/10b Decoder

Receive

2

Not applicable

5.

Symbol Alignment

Module

Receive

2

Not applicable

6.

Deskew Module

Receive

FIFO_Threshold + 5

Not applicable

7.

EFIFO Module

Receive

FIFO threshold + 7 +

no_of_lanes_bonded/4*

Not applicable

8.

Other

2

Total Latency

13 (max)

2

* For special case of lane-bonding

UG028, July 1, 2014

43