Interface encapsulation, Pcs self test checker – Achronix Speedster22i SerDes User Manual

Page 32

the 20-bit mode of operation, the most significant 20-bits of data are placed on bits 19:0 of the

barrel shifter and the least significant 20-bits are discarded. The 6-bit select control can select

a range of active bits, from [19:0] (for a select value of 0x00) to [82:63] (for a select value of

0x3F).

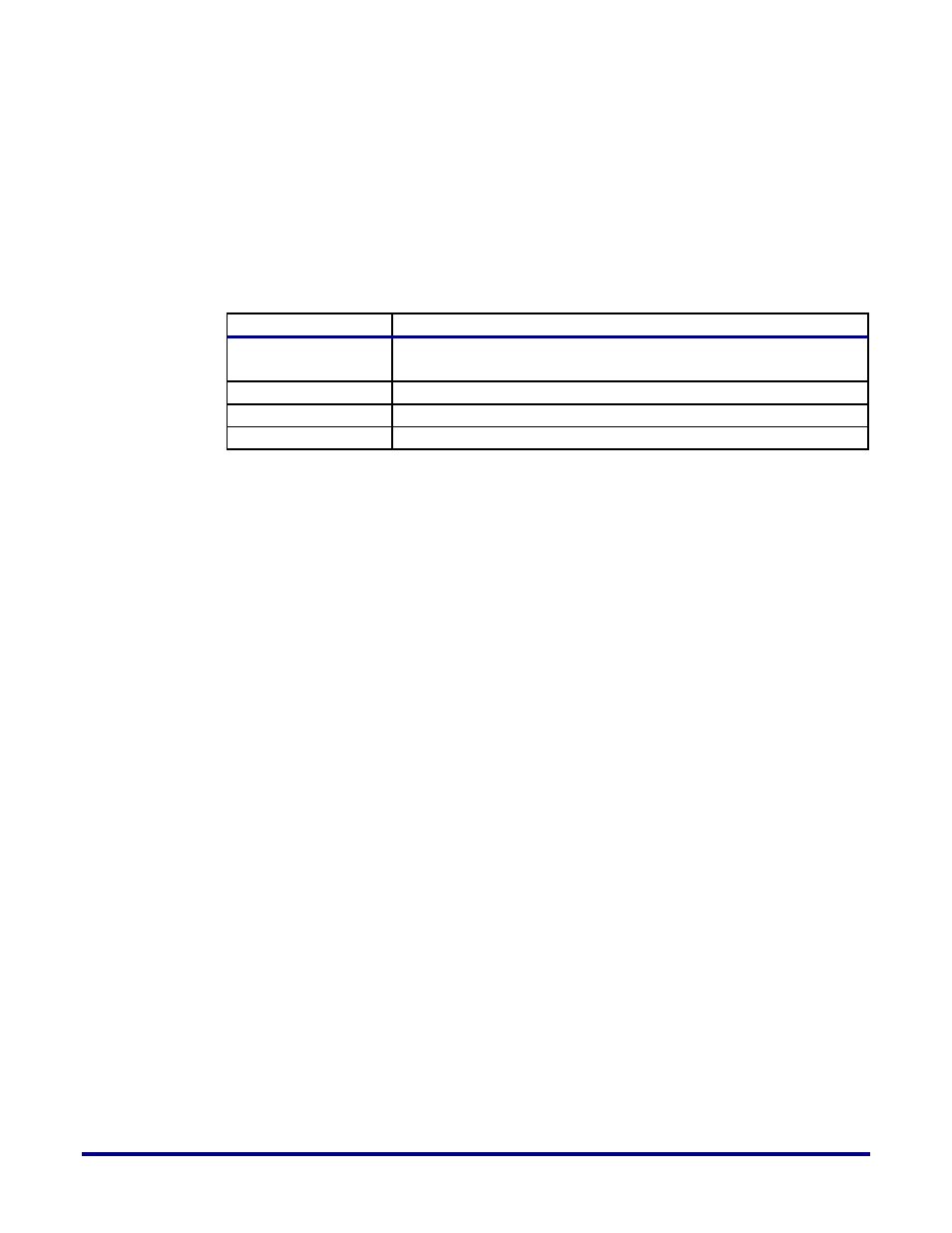

“Table 4: List of Important Interface Signals for bit slider”, provides a list of important

interface signals used for bit slider.

Table 4: List of Important Interface Signals for bit slider

Port

Description

bit_range_sel[5:0]

Primary input from SerDes. Used to select data window for

removing bit skew

bit_slider_enable

Register bit[1] @’h092 to enable bit-slider

word_mode

Register bit[3] @’h000 to select data path width – 1 word or 2 word

8bit_mode

Register bit[2] @’h000 to select type of encoding - 8(16) or 10(20)

Interface Encapsulation

This block encapsulates the protocols before passing data to the fabric. Details on the

standards supported by Achronix FPGA can be found in Section –“PCS Interface”.

PCS Self Test Checker

When PCS self-testing feature is used, this block checks for the correctness of the receive data.

Details on this block are available in “PCS Test Pattern Generator” and “PCS Test Pattern

32

UG028, July 1, 2014