Figure 40 – Achronix Speedster22i SerDes User Manual

Page 91

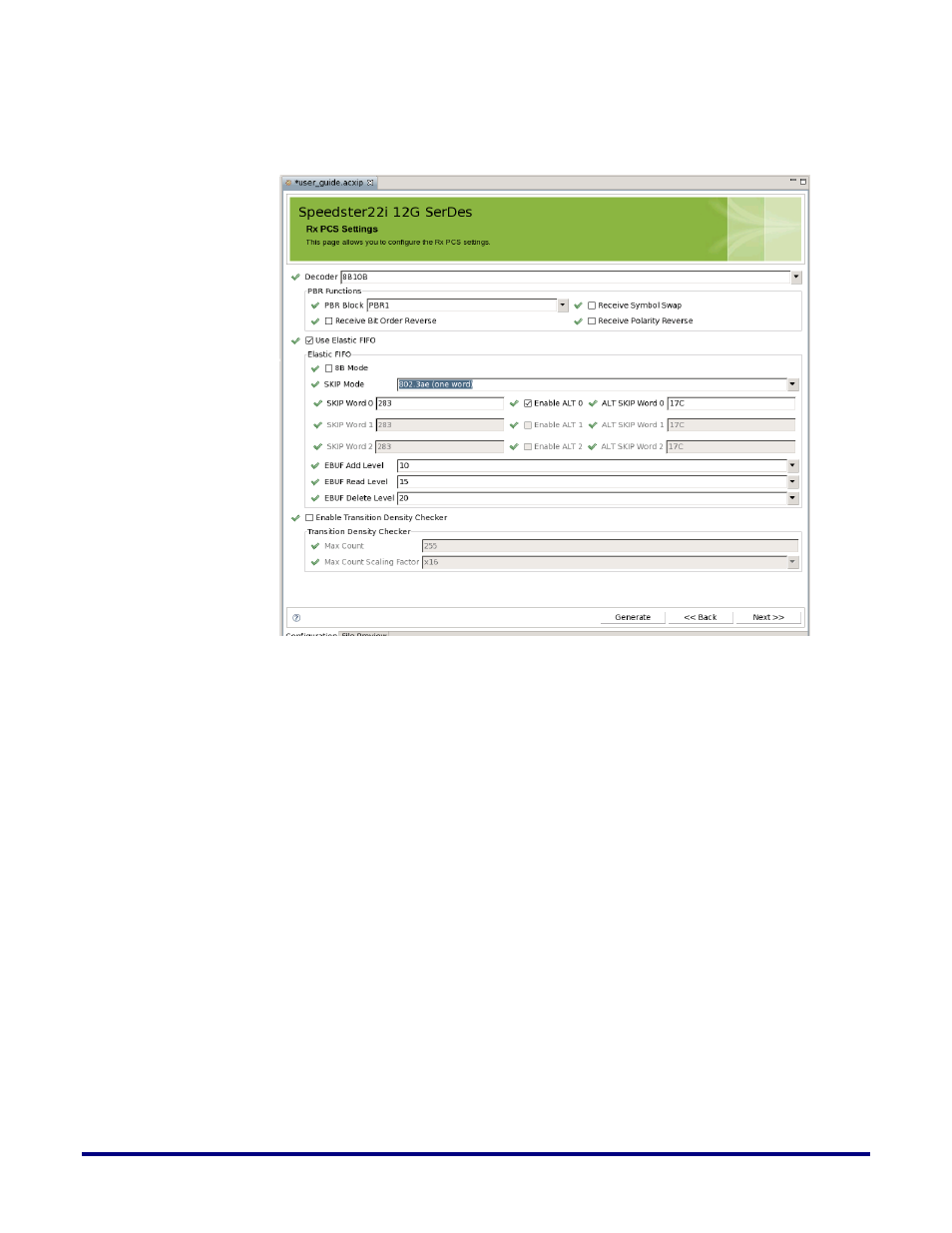

Figure 40: PCS Settings for Receiver – Configurations for Decoder and Elastic FIFO

Now, just as we did for the design without clock-compensation (simple_serdes_design), we

can generate the design files from the ACE GUI for our design with clock compensation

(simple_serdes_design_efifo).

Modification – 2 (RTL Code): The comma character that has previously been used for symbol

alignment is used as EFIFO SKIP word in this derivative of the design. Therefore, no change

is required for the data generation module (data_gen.v).

However, with clock compensation enabled, the aligned TX and RX clocks are available from

the SerDes instance, as a single clock. Top-level design needs to be modified to reflect this.

More specifically, in the baseline design simple_serdes_design, two clocks were generated by

SerDes: ln0_TX_clk and ln0_RX_clk. These two clocks had respectively been used on the

transmitter side (such as data generation) and on the receiver side (such as data check). In

contrast, for the current derivative of the baseline design (simple_serdes_design_efifo), one

clock .ch0_o_TX_data_clk is used as the clock from SerDes.

UG028, July 1, 2014

91