Receiver (rx)/transmitter (tx), Digital pma (dpma), Figure 4: synthesizer architecture – Achronix Speedster22i SerDes User Manual

Page 14

2. Receiver (RX)/Transmitter (TX)

The RX/TX block consists of the following circuits:

•

TX buffer: Converts single-ended signal to differential and performs equalization on

(or pre-emphasis) the outgoing serial signal

•

RX buffer: Converts differential signal to single ended and performs equalization on

incoming signal using Continuous Time Linear Equalizer (CTLE) and Decision

Feedback Equalizer (DFE)

•

Clock Data Recovery (CDR): Recovers clock and data from the incoming signal for

deserialization

•

On-Chip Scope: Used for plotting an eye of the incoming signal post equalization for

debug

•

Serializer/Deserializer: Converts parallel data to serial data using a high speed clock

from the synthesizer

3. Digital PMA (DPMA)

The DPMA block consists of the following circuits:

•

Calibration: Performs calibration of all the analog circuits using trim settings and

offsets

•

PMA BIST: Includes PRBS 7, 23, 31 and 40-bit user defined pattern generators and

checkers Power management

•

Configuration registers (Memory)

•

JTAG and Boundary Scan

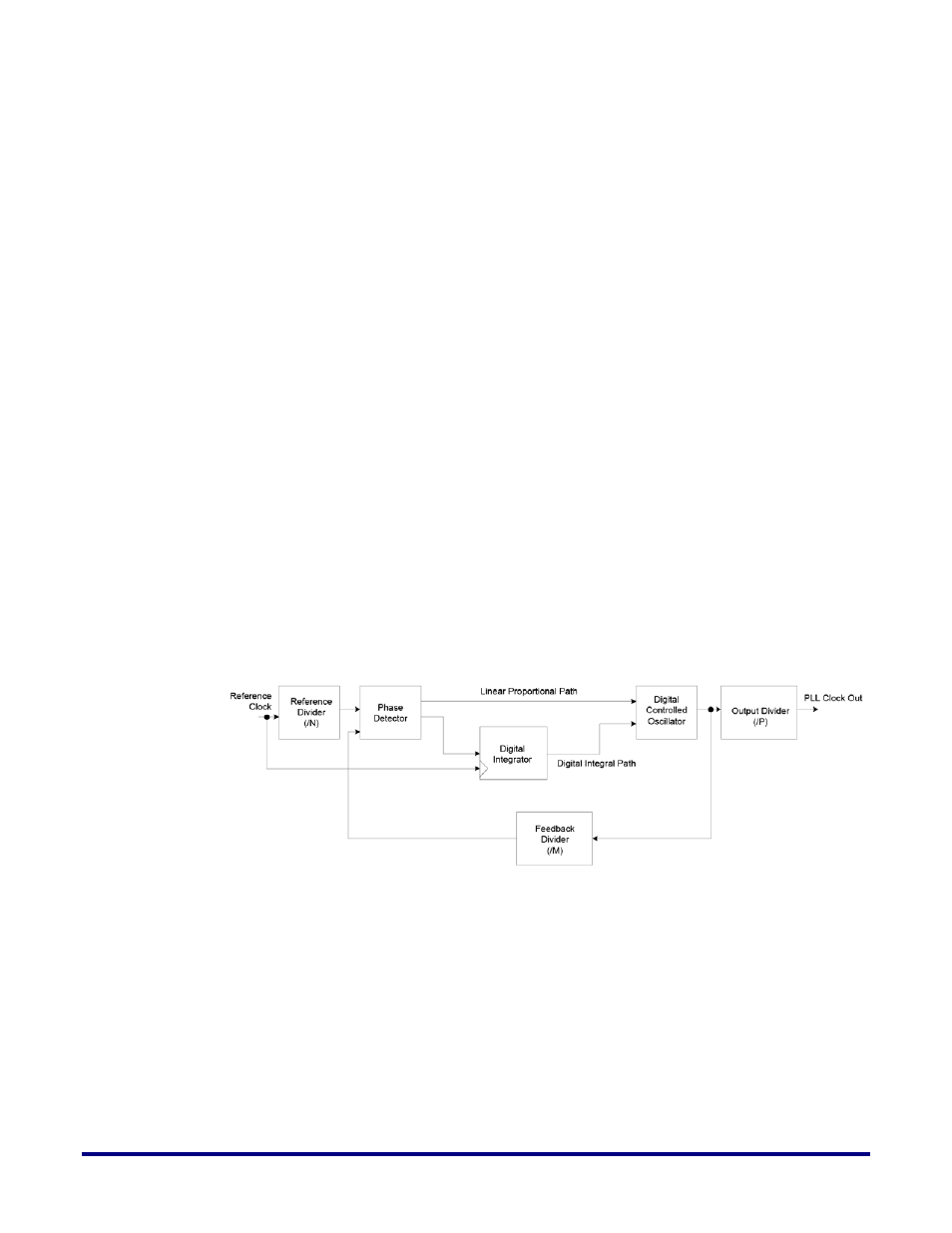

Figure 4: Synthesizer Architecture

14

UG028, July 1, 2014