Table 19: tx pcs settings – Achronix Speedster22i SerDes User Manual

Page 69

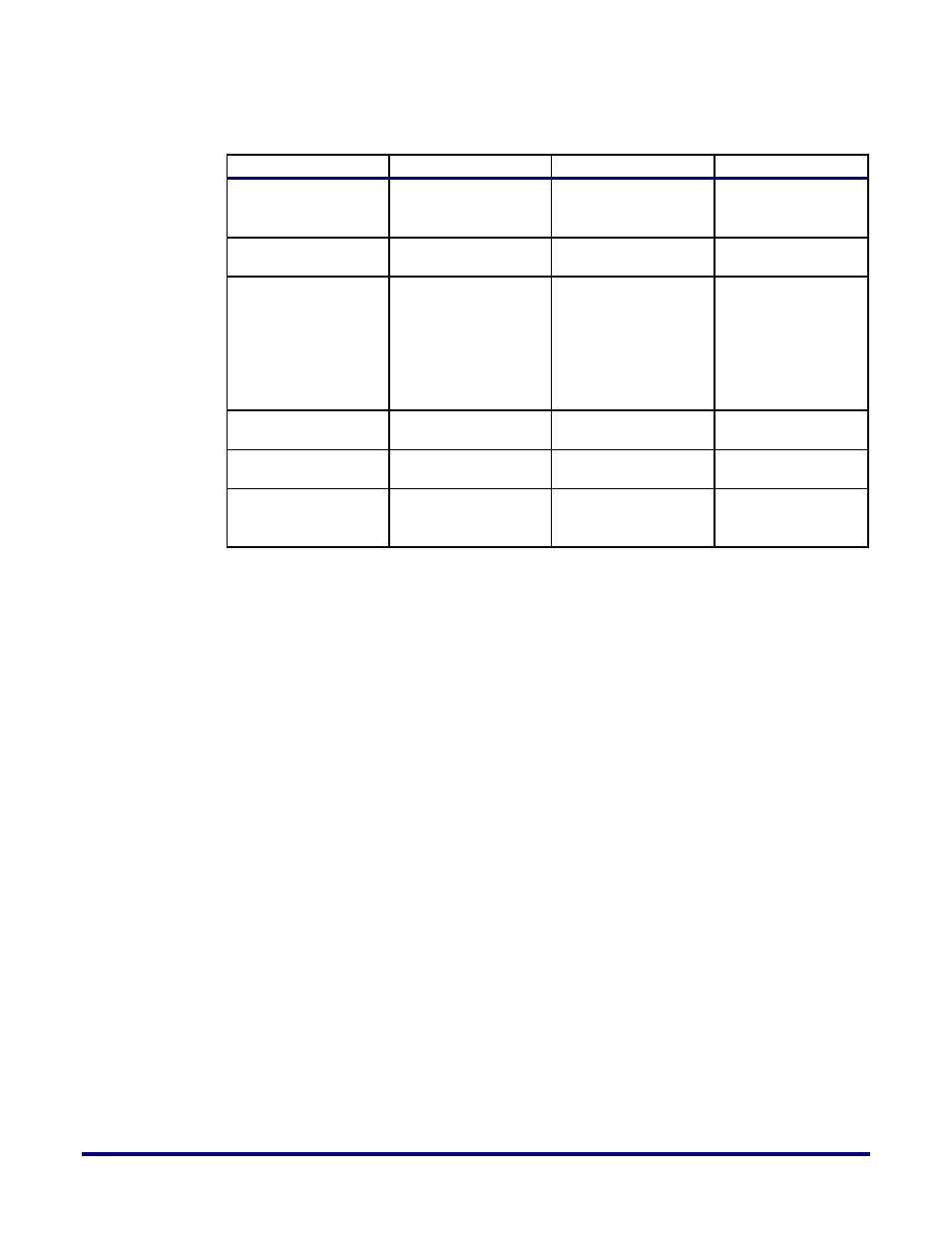

Table 19: TX PCS Settings

Entry field

Purpose

Available Options

Choice made

Encoder

•

Disabled

•

8b/ 10b

•

128/130b

8B10B

PBR Functions

PBR Block

Whether PBR block is

used. PBR0 is used on

data before encoder (or

when encoder is

disabled). PBR1 is used

on encoded data to

PMA.

•

PBR0

•

PBR1

PBR0

Transmit Symbol Swap

Setting for PBR block

on TX path.

•

True

•

False

False

Transmit Bit Order

Reverse

Setting for PBR block

on TX path.

•

True

•

False

False

User-Controlled

Disparity and Error

Forcing

Option to force

disparity and error

forcing (from fabric?)

•

True

•

False

False

Clicking Next on the window titled “TX PCS Settings” will bring the windows for BIST test

settings. We will ignore those windows for this design.

Section on Manually Overriding PMA/PCS Register Values:

Based on the user choices made in the earlier sections, ACE has assigned the values for PMA

and PCS registers at this point. The advanced user however may want to change the pre-

defined value for one or more registers. This section of ACE GUI provides this option for

advanced users.

Please refer to the Section - Bypassing PCS by Manually Overriding Corresponding Register

for further details on this.

UG028, July 1, 2014

69