Achronix Speedster22i SerDes User Manual

Page 73

iSerDes is chosen as the Hierarchical Instance Path, the generated .sdc and .pdc files need not

be modified.

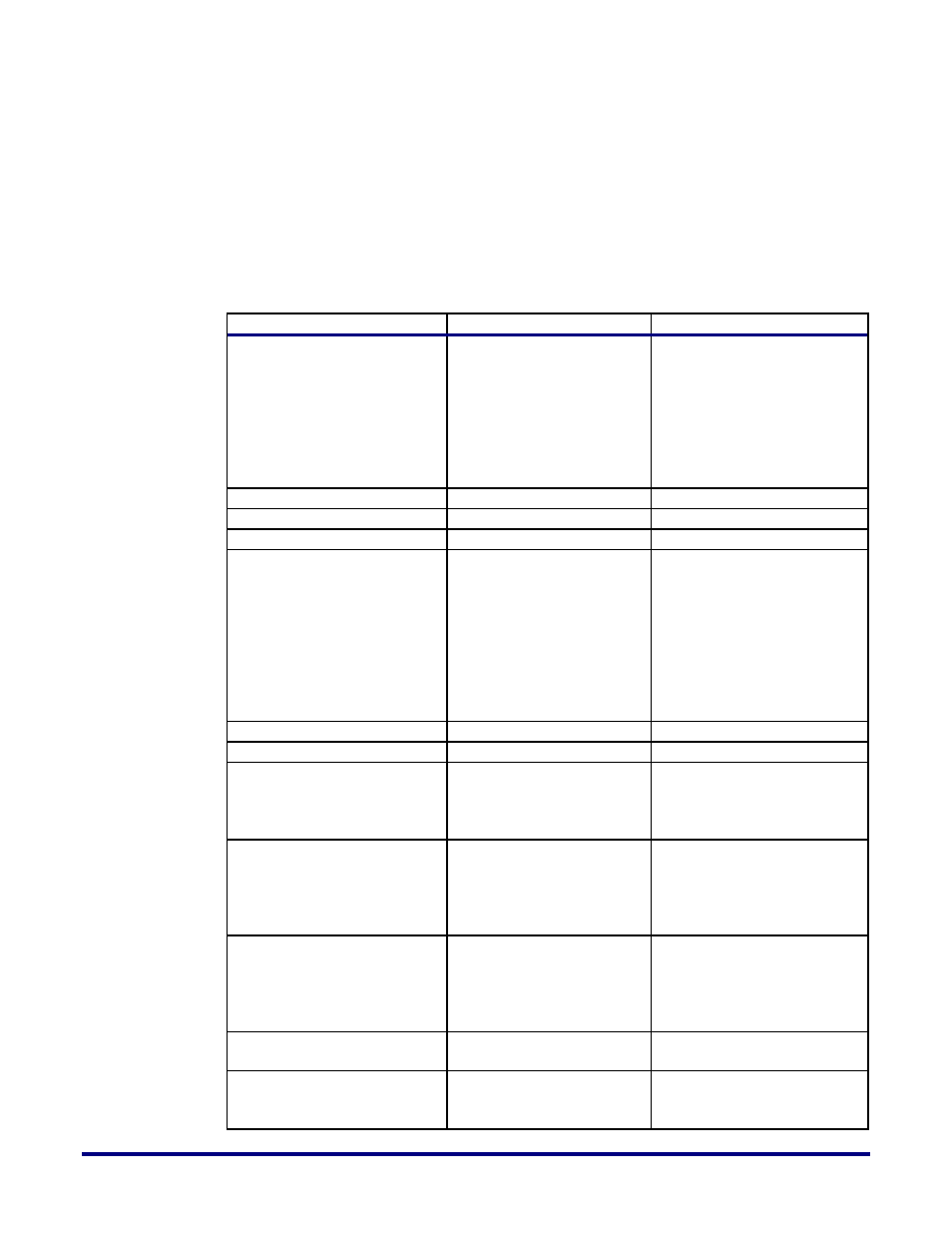

“Table 20: Signals passed between the SerDes Instance and the Top-Level module” gives a

list of the ports in the SerDes wrapper that are accessed from the top-level module of the

current design. The corresponding signal names used in the top-level module are also listed

in this Table.

Table 20: Signals passed between the SerDes Instance and the Top-Level module

SerDes Port Name

Top-level Signal-name

Comments

ch0_i_ba_RX_m

ln0_RX_m

These input signals to SerDes

are also inputs to the top-level

RTL. Note: These signals are

connected directly from SerDes

to the package balls without

any logic in between. In other

words, the users don’t need to

insert any I/O pads.

ch0_i_ba_RX_p

ln0_RX_p

ch0_i_bck_ref_m

ln0_refclk_m

ch0_i_bck_ref_p

ln0_refclk_p

ch0_i_RX_rst_n

1

ln0_rst_n_RX

Reset inputs to the SerDes from

user logic.

Note: Same input can be used

for RX and TX reset signals.

These signals should preferably

be delayed from the hard-reset

signal. Hard reset goes to the

PMA and RX and TX resets go

to the PCS.

ch0_i_TX_rst_n

1

ln0_rst_n_TX

ch0_i_rst_hard_n

1

ln0_rst_hard

ch0_i_TX_datain

ln0_TX_data

Transmit data input to SerDes

from user logic. (Refer to

data_generation.v presented

later.)

ch0_o_RX_data_clk

ln0_RX_clk

Output from SerDes to user

logic. RX-clock generated from

SerDes and used for RX-path in

top-level, such as the checker

for the received data.

ch0_o_TX_data_clk

ln0_TX_clk

Output from SerDes to user

logic. TX-clock generated from

SerDes and used for TX-path in

top-level, such as generator for

the transmitted data.

ch0_o_RX_dataoutA

ln0_RX_data

Receive side RX data output

from SerDes to the user logic.

ch0_o_pma_RX_cdr_lck2dat

ln0_pma_RX_cdr_lck2dat

Outputs from SerDes.

These are status signals from

SerDes. These signals indicate

UG028, July 1, 2014

73