Achronix Speedster22i SerDes User Manual

Page 54

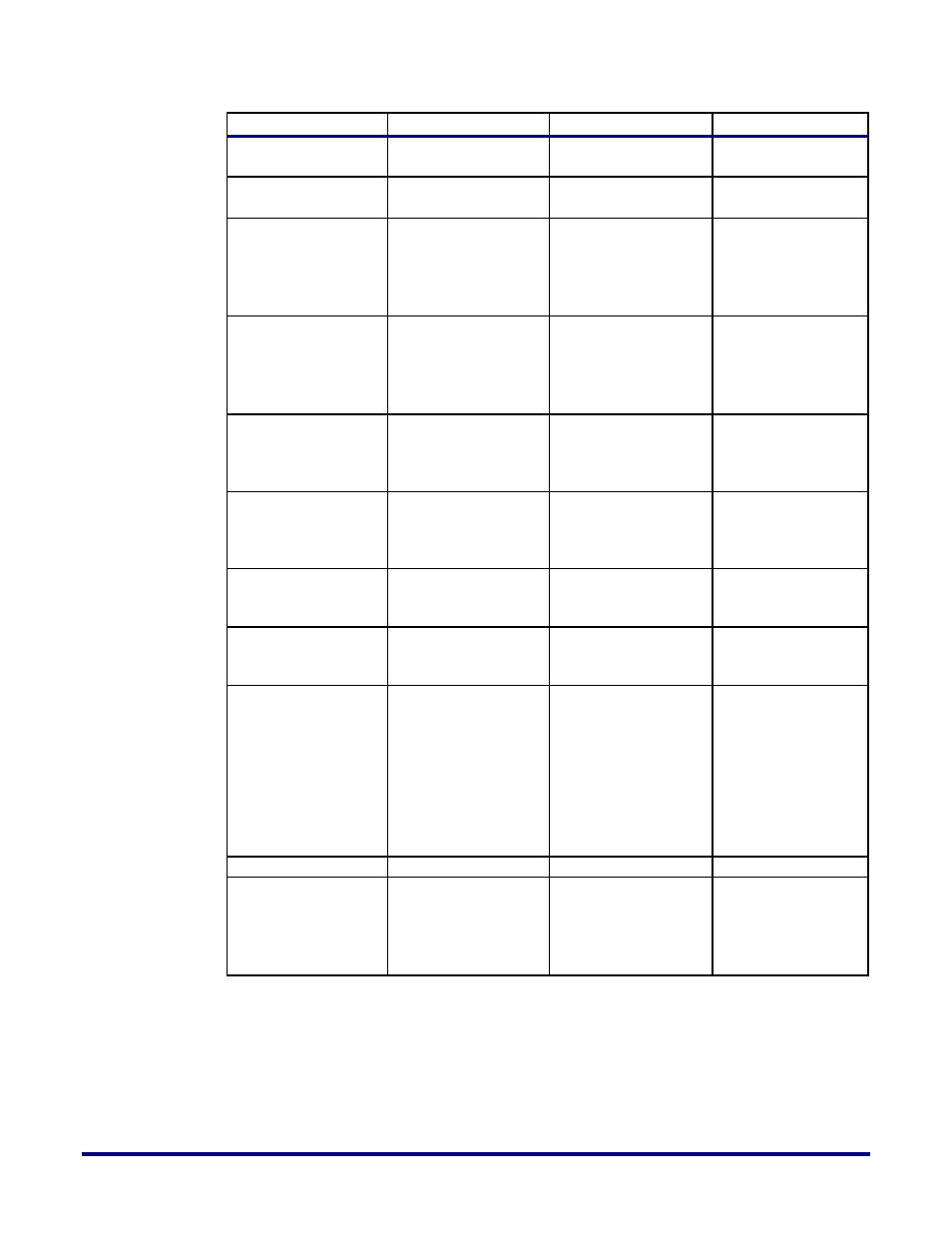

Entry field

Purpose

Available Options

Choice made

Number of Lanes

Number of lanes used

by the design

1 to 12.

1

TX Data Rate (Gbps)

TX data rate for the

design

12 options ranging

from 1.0265 to 11.31

*1

10.3125

RX Data Rate (Gbps)

RX data rate for the

design is currently

disabled. ACE GUI

makes it equal to the

TX Data Rate.

*1 *3

Ref. Clock (MHz)

Reference clock for

SerDes PLL’s.

18 options ranging

from 60MHz to 350

MHz, including the

reference frequency for

typical protocols.

*1

156.25 MHz

RX Termination

Termination resistance

used for Receive Path

•

Disconnect

•

85

•

100

•

120

100

TX Termination

Termination resistance

used for Transmitter

Path

•

Disconnect

•

85

•

100

•

120

100

Data Width

Defines the number of

data bits used by the

SerDes interface

•

16

•

20

20

Operating Mode

Whether the SerDes

will be used for RX or

TX or both.

•

RX only

•

TX only

•

TX and RX

TX and RX

Enable Channel

Bonding

Whether the design

uses bonded lanes

•

True

•

False

The check-box is

enabled only when the

design uses multiple

lanes. The user must

use lane-bonding if

number of lanes is

more than 4.

Not applicable for

single-lane

simple_serdes_design

Placement:

Chip Edge

Defines the location of

the SerDes lane used.

•

North

•

South

Implies the North and

South sides of Achronix

FPGA

*2

North

54

UG028, July 1, 2014