Achronix Speedster22i SerDes User Manual

Page 74

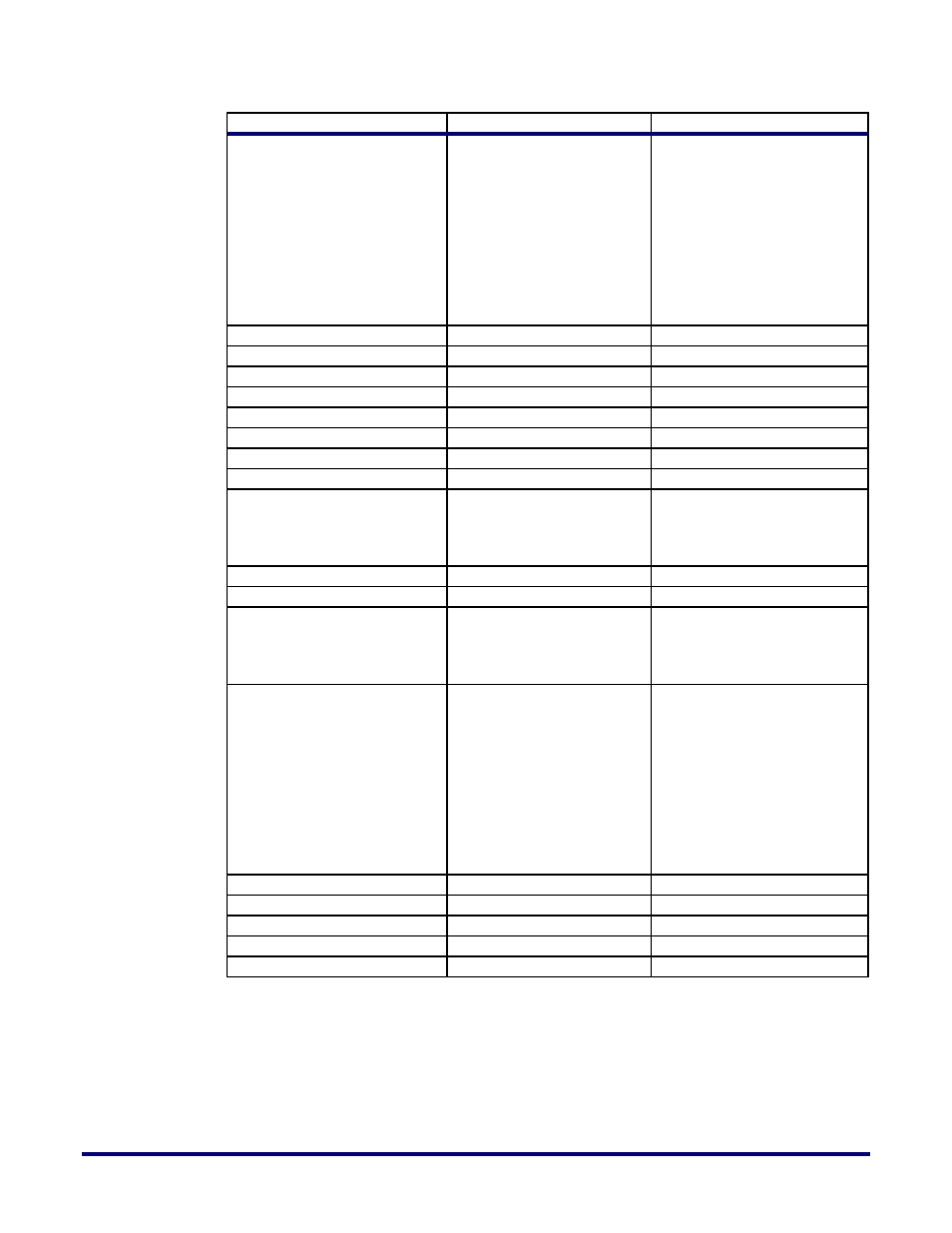

SerDes Port Name

Top-level Signal-name

Comments

whether the SerDes is ready.

For instance, ln0_TX_ready

indicates that the SerDes is

ready for data receipt.

These signals can be used for

debugging and other purposes.

For instance, ln0_TX_ready can

be used to start data

transmission.

ch0_o_pma_TXready

ln0_pma_TXready

ch0_o_pma_synthready

ln0_pma_synthready

ch0_o_pma_RXready

ln0_pma_RXready

ch0_o_pma_RXstat

ln0_pma_RXstat

ch0_o_pma_sig_detect

ln0_pma_sig_detect

ch0_o_pma_synthstat

ln0_pma_synthstat

ch0_o_pma_TXstat

ln0_pma_TXstat

ch0_i_pipe_pd

2’b0

ch0_i_RX_iddq_n

1

ln0_i_RX_iddq_n

Power on reset signals for PMA.

Signals can be sent to assert

these inputs certain time after

the SerDes is powered up.

ch0_i_synth_iddq_n

1

Ln0_i_synth_iddq_n

ch0_i_TX_iddq_n

Ln0_i_TX_iddq_n

ch0_o_RX_syma_locked

ln0_RX_syma_locked

Output from SerDes to user

logic. Indicates symbol

alignment, when the module is

used.

ch0_i_sbus_clk

i_sclk

Input clock-signal to the SerDes

for use with the Serial Bus

(SBUS). In this design, it is

coming from a top-level IO

clock pad. The external SBUS

clock must be running when

you program this design into

the device since the SBUS is

access in the startup sequence

to enable loopback.

ch0_i_sbus_data[1:0]

ln0_sbus_wrdata

sbus-related signals.

ch0_i_sbus_req

ln0_sbus_req

ch0_i_sbus_sw_rst

ln0_sbus_sw_rst

ch0_o_sbus_ack

ln0_sbus_ack

ch0_o_sbus_data[1:0]

ln0_sbus_rddata

1

These signals are part of the reset sequence and are further detailed in the section: Reset

Sequence.

Based on the table above, the user can now instantiate the SerDes module into top-level RTL.

74

UG028, July 1, 2014