Pcs blocks in the receiver (rx), Transition density checker (tdc), Figure 13: pcs receive block overview – Achronix Speedster22i SerDes User Manual

Page 22

PCS Blocks in the Receiver (RX)

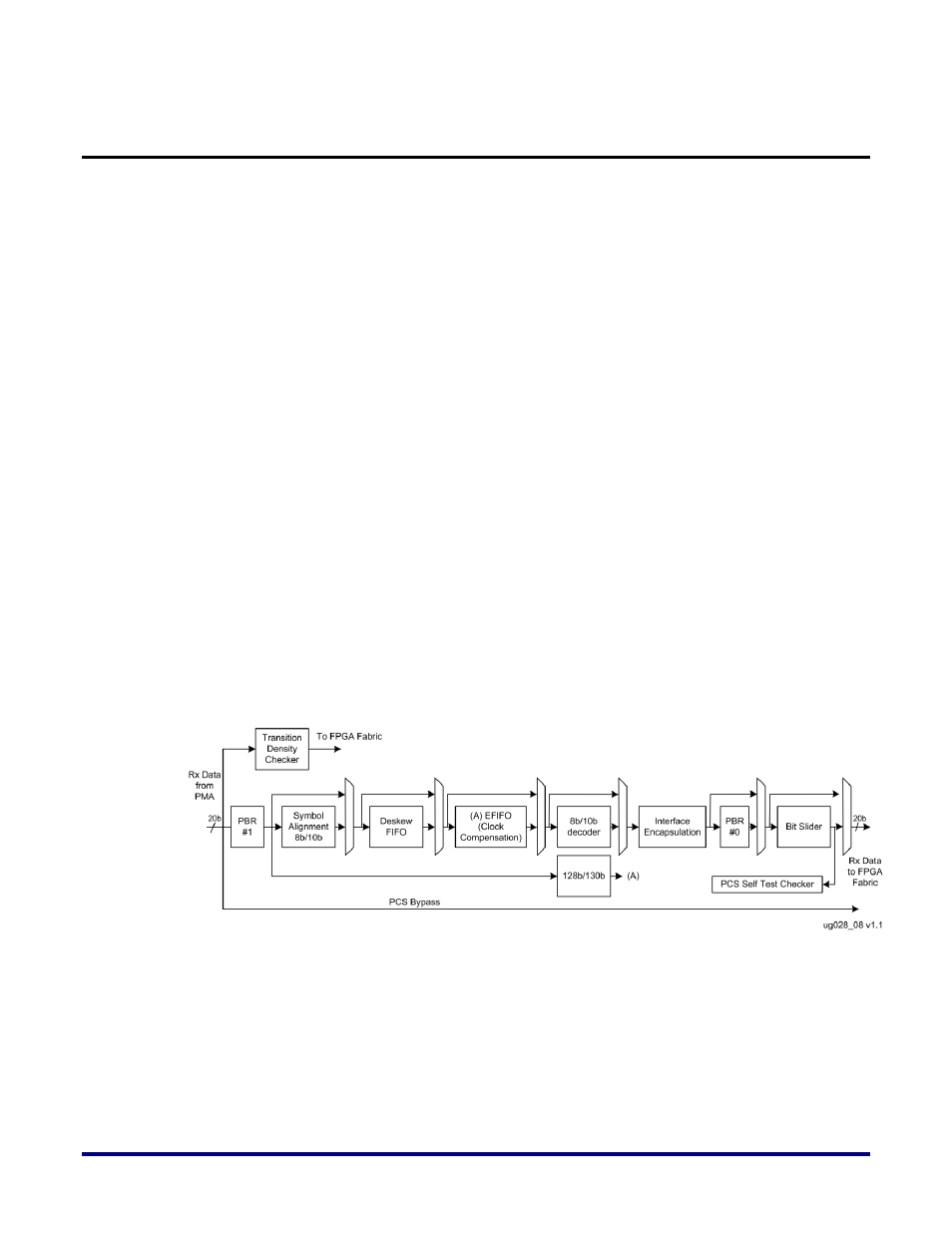

This chapter describes the PCS components on the receiver data path. The functional block

diagram of the receiver is shown in “Figure 13: - PCS Receive Block Overview”. The key

blocks in the RX-PCS include:

•

Transition Density Checker (TDC): Generates a trigger bit when the number of

consecutive 1’s or 0’s reaches a pre-defined value.

•

Polarity Bit Reversal (PBR): Inverts data, swaps byte ordering and reverses bit-

ordering, if used on the TX data path.

•

Symbol Alignment: Uses alignment characters and sequences to define the symbol

boundary on the incoming data-stream.

•

Decoders: Generates 8-bit code group and 1-bit control signal from the 10-bit

encoded (received) data.

•

Deskew First-In-First-Out (FIFO): Synchronizes the data received across the lanes

when lane-bonding is used.

•

Clock Compensation (Elastic FIFO): Synchronizes the data received on PMA at

recovered clock domain with a system clock (typically the transmit clock).

•

Bit Slider: Takes care of bit-wise skew from the fabric, when used.

•

PCS Interface Encapsulation: Provides interface with the fabric. Supports Gigabit

Ethernet, XAUI, Pipe and 10G Ethernet interfaces.

•

PCS Self Test Checker: Self checking module, detailed in Chapters “PCS Test Pattern

Generator” and “PCS Test Pattern Checker”

The main features for the supported standards in the PCS side can be found in Chapter

Figure 13: PCS Receive Block Overview

Transition Density Checker (TDC)

The transition density checker monitors the parallel RX data bus from the PMA and monitors

the number of consecutive 0s or 1s, called run length. If the number reaches a pre-configured

value, the checker sets a trigger bit to indicate the transition density violation. This pre-

configured value is called threshold and the minimum threshold programmed is half the

width of data path. In case scaling is used the actual threshold effective will be the one shown

22

UG028, July 1, 2014