Achronix Speedster22i SerDes User Manual

Page 89

Overview of the modification: With respect to the steps followed in creating

simple_serdes_design, the following modifications are made in preparing

simple_serdes_design_efifo:

1. Changes in using ACE GUI during wrapper generation.

2. Changes in RTL code related to using clock signals generated by SerDes.

3. Changes in ace_placement.pdc and ace_constraint.sdc related to using clock signals from

SerDes.

These modifications are detailed below.

Modification – 1 (ACE GUI): In the design discussed above (simple_serdes_design), clock

compensation (EFIFO) was disabled. For the current derivative of the design

simple_serdes_design_efifo, EFIFO is enabled.

We will start by creating a new ACXIP file in the ACE GUI for the modified design,

simple_serdes_design_efifo. All fields in the GUI can be set to the same values as was done for

simple_serdes_design, wit hthe exception of the RX PCS Setings as shown below. The entry

fields and the available options are listed in “Table 21: Modifications for

simple_serdes_design_efifo (RX PCS Settings)” This table also presents the choices that are

made for the current design: simple_serdes_design_efifo.

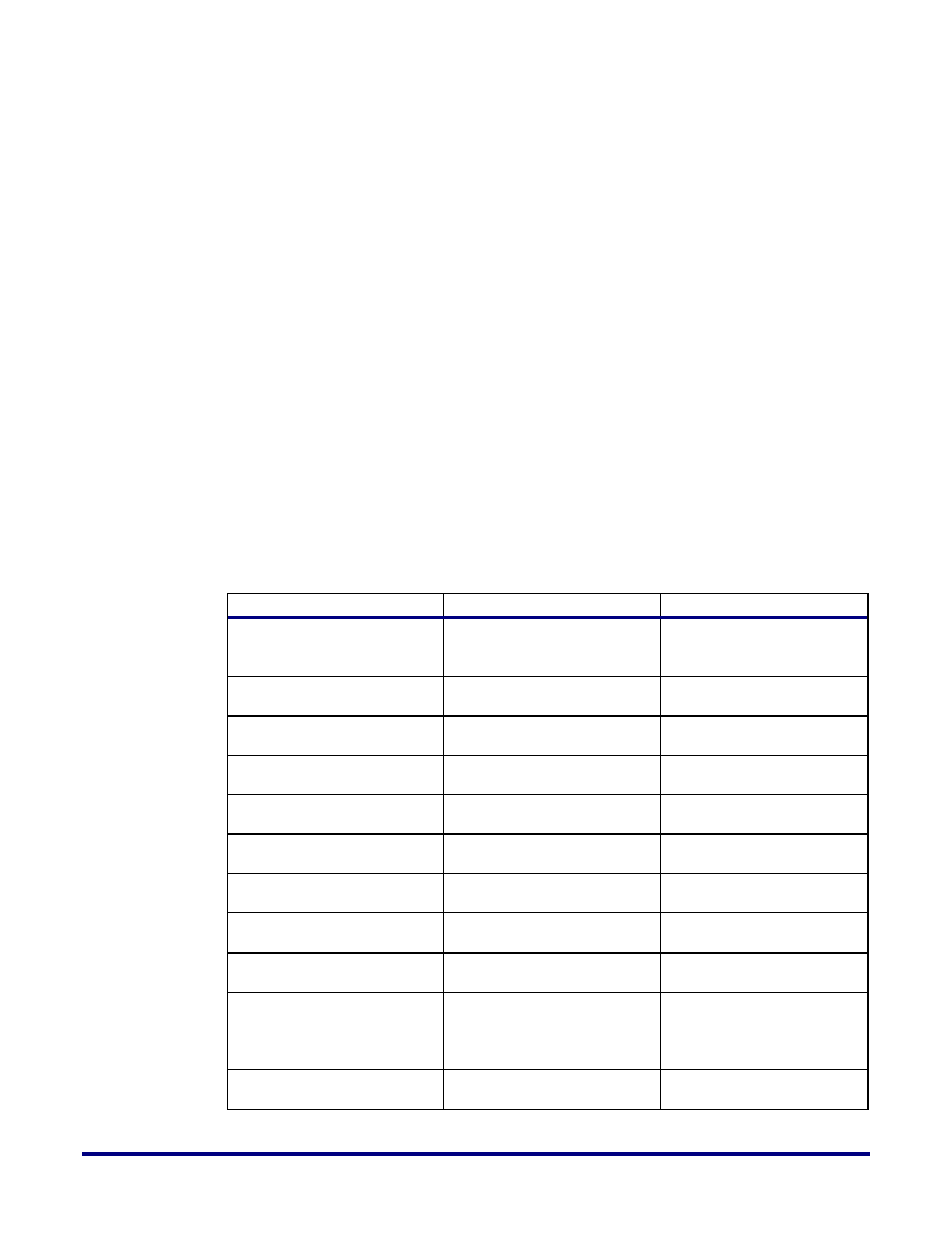

Table 21: Modifications for simple_serdes_design_efifo (RX PCS Settings)

Entry field

Available Options

Choice made

Decoder

*3

•

Disabled

•

8b/10v

•

128/130b

8B10B (8b/10b) decoder

Polarity Bit Reversal (PBR)

Functions

PBR Block

*3

•

PBR0

•

PBR1

PBR0 (Default)

Receive Symbol Swap

*3

•

True

•

False

False

Receive Bit Order Reverse

*3

•

True

•

False

False

Receive Polarity Reverse

*3

•

True

•

False

False

Elastic FIFO

*3

Use Elastic FIFO

*3

•

True

*2

•

False

True

8b Mode

*3

•

True

•

False

False

SKIP Mode

*3

•

Disabled

•

802.3ae (one word)

•

802.3 (two words)

•

PCIe

802.3ae (one word)

SKIP Word 0

*3

Text field to select user-defined

value

10’h283

UG028, July 1, 2014

89