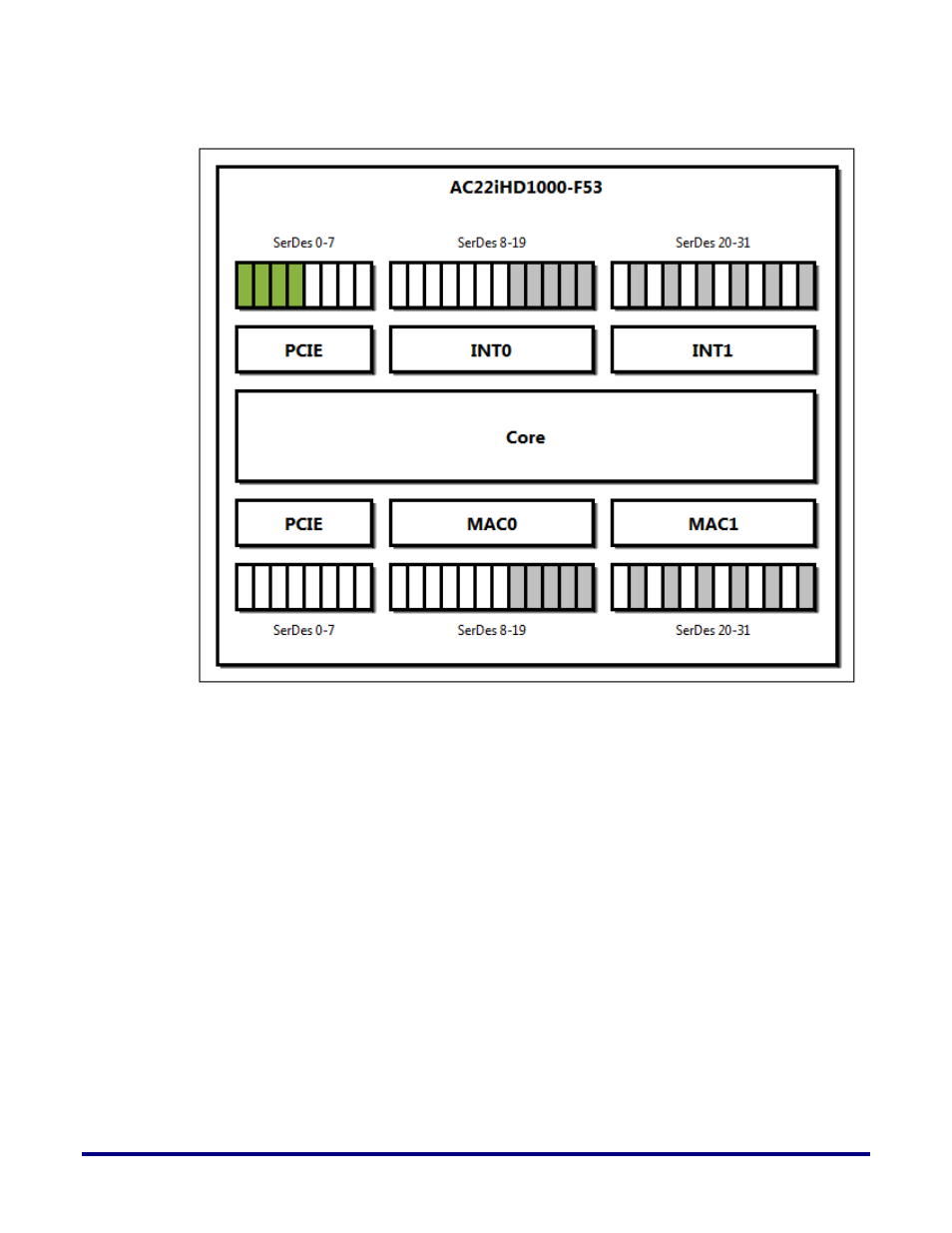

Figure 39: serdes placement guidelines – Achronix Speedster22i SerDes User Manual

Page 85

Figure 39: SerDes Placement Guidelines

•

Avoid lanes 15-19 (on North and South) when not using channel bonding, since these

lanes consume clock resources in both East and West clock regions. This is not a

hard rule, but is something to be aware of when calculating clock resources.

Example of managing clock resources:

Let’s say we want to use all 32 SerDes lanes on the North side of the chip. We will not be

using the hard IP controllers. We need to have 8 independent non-bonded raw SerDes lanes

running at 5 Gbps, and the other 24 lanes can optionally use channel bonding and run at 10

Gbps.

To start with, remember that there are 16 clock resources available in the NorthWest clock

region and another 16 clock resources available in the NorthEast clock region.

If we simply instantiate 8 raw SerDes at 5 Gbps, we will get 16 clock resources entering the

Core: 1 Rx Data Clock and 1 Tx Data Clock for each lane. We can reduce this to 8 clocks by

enabling the PCS EFIFO Elastic Buffer to combine Tx and Rx clocks.

Next, if we were to instantiate the 24 10 Gbps lanes independently, we would get a total of 96

clocks entering the Core: (1 Rx Data Clock and 1 Tx Data Clock for each lane) x 2 for Wide

Bus. This is far too many clocks. We can reduce this with channel bonding. Since channel

bonding is limited to a maximum of 12 lanes per group, let’s create 2 bonded groups of 12

UG028, July 1, 2014

85