An269 – Cirrus Logic AN269 User Manual

Page 60

60

AN269REV1

AN269

The first step in setting up the EP93XX raster engine for this display involves determining the proper

SPCLK rate. Using the following equations:

tHORIZ = tHACTIVE + tHFRONTPORCH + tHSYNC + tHBACKPORCH

tHORIZ = 80 + 2 + 1 + 7 = 90 (SPCLK periods)

tVERT = tVACTIVE + tVFRONTPORCH + tVSYNC + tVBACKPORCH

tVERT = 240 + 0 + 0 + 0 = 240

fVSYNC = 70 Hz

SPCLK = tHORIZ * tVERT * fVSYNC

SPCLK = 90 * 240 * 70 = 1512000 SPCLK periods per second (1.5 MHz)

Now that the SPCLK rate is known, the source of that clock must be determined. This is done using the algorithm.

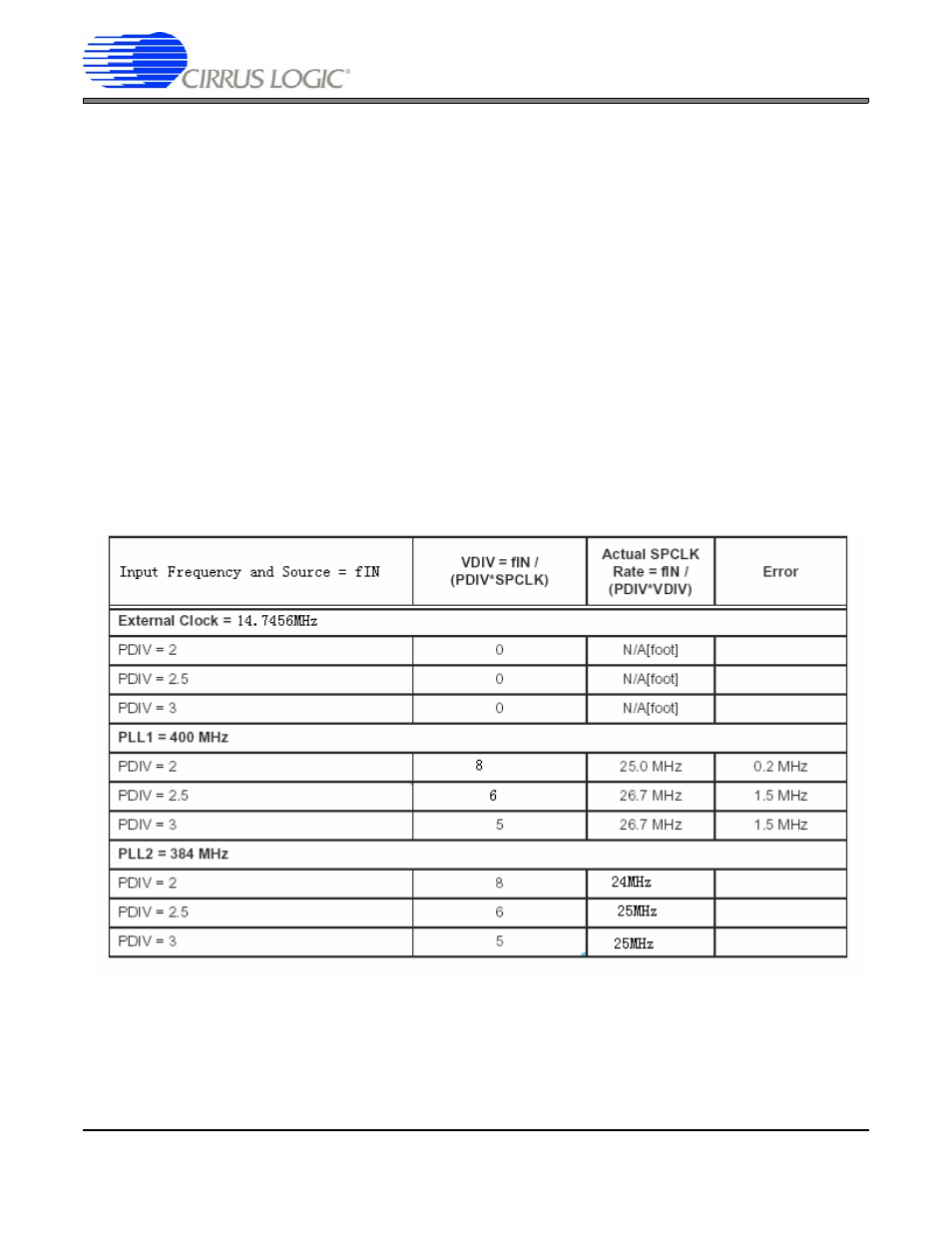

For this example we will use the actual frequency (not 2x the frequency) and the possible PDIV values of 2, 2.5, and

3. This yields possible values of VDIV. Using those values as PDIV and VDIV, we can compute the error in SPCLK

by subtracting the desired value of SPCLK (1.478 MHz). Assuming an external clock rate of 14.745600 MHz,

PLL1=400 MHz, PLL2=384 MHz, we come up with the following table of values:

Table 19. Possible SPCLK Sources for HOSIDEN HLAM6323