An269 – Cirrus Logic AN269 User Manual

Page 33

AN269

AN269REV1

33

A timing diagram for this type of display is shown in

. Signal and timing names are those of the

corresponding EP93xx pins. A description of the timing requirements is given in

In this type of display, the total number of SPCLKs per horizontal line is equal to the horizontal resolution.

Also, and the total number of SPCLKs per full video frame is the horizontal resolution times the vertical res-

olution. Unlike an HSYNC/VSYNC-style display, there are no “extra” HSYNC or SPCLK pulses in the frame.

This will be accomplished by using a gated SPCLK, controlled by the HClkStrtStop register.

Note that in this timing, the VCSYNC signal comes before the HSYNC signal. To accomplish this, the hori-

zontal line counter should be aligned such that the line transition occurs at the VCSYNC transitions. More

on this will be illustrated when the horizontal and vertical timings are determined.

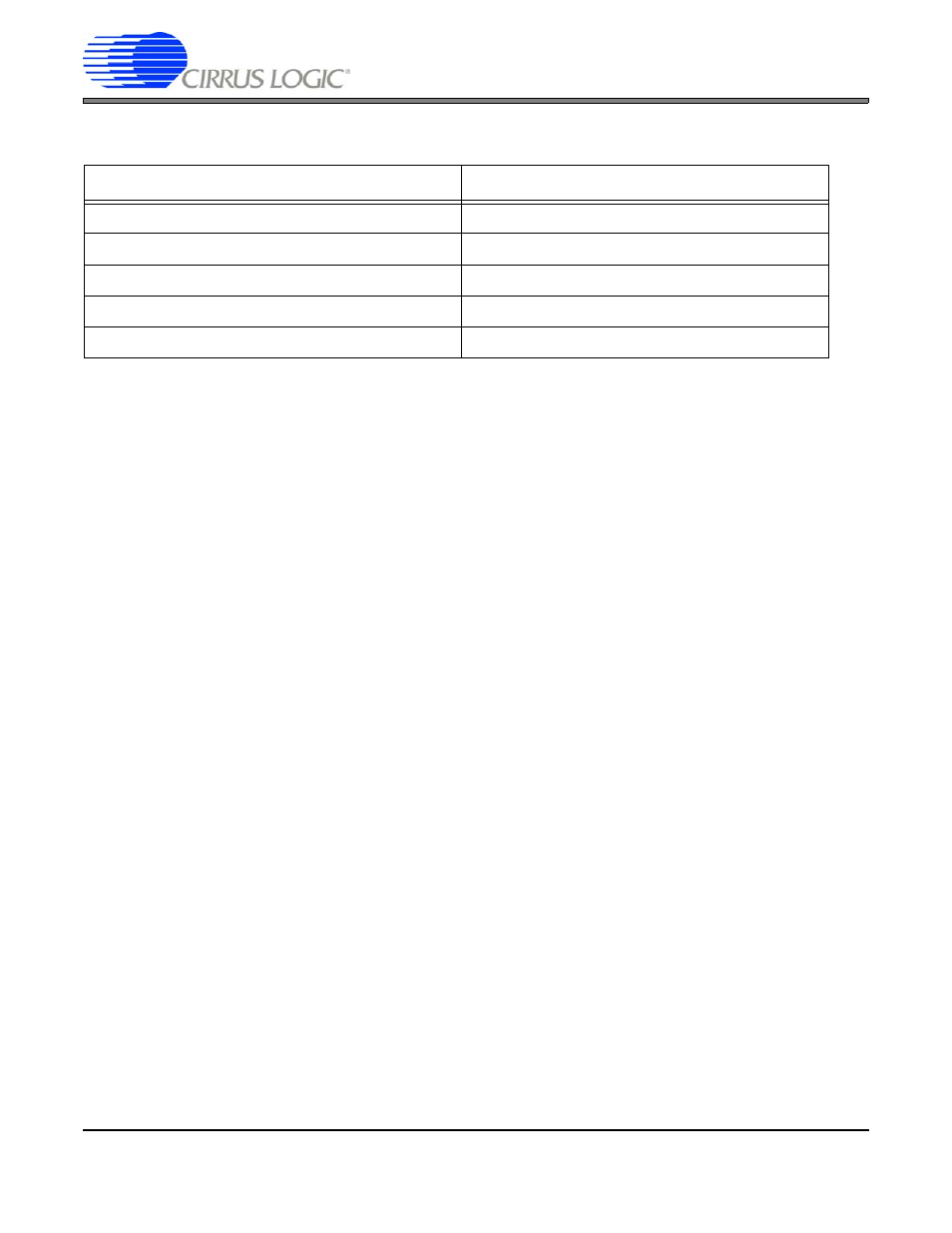

Timing Parameter

Description

tHSYNCH

HSYNC High pulse duration

tVCHHSYNC

Time from VCSYNC High to HSYNC low

tSPCLKHSYNC

Time from last SPCLK to HSYNC High on next line

tHSYNCSPCLK

Time from HSYNC Low to first SPCLK

tVCLHSYNC

Time from VCSYNC Low to HSync Rising Edge

Table 7. Frame Type 2 Relevant Timing Parameters