Splay, see, Example hsync/vsync-style lcd display, An269 – Cirrus Logic AN269 User Manual

Page 52

52

AN269REV1

AN269

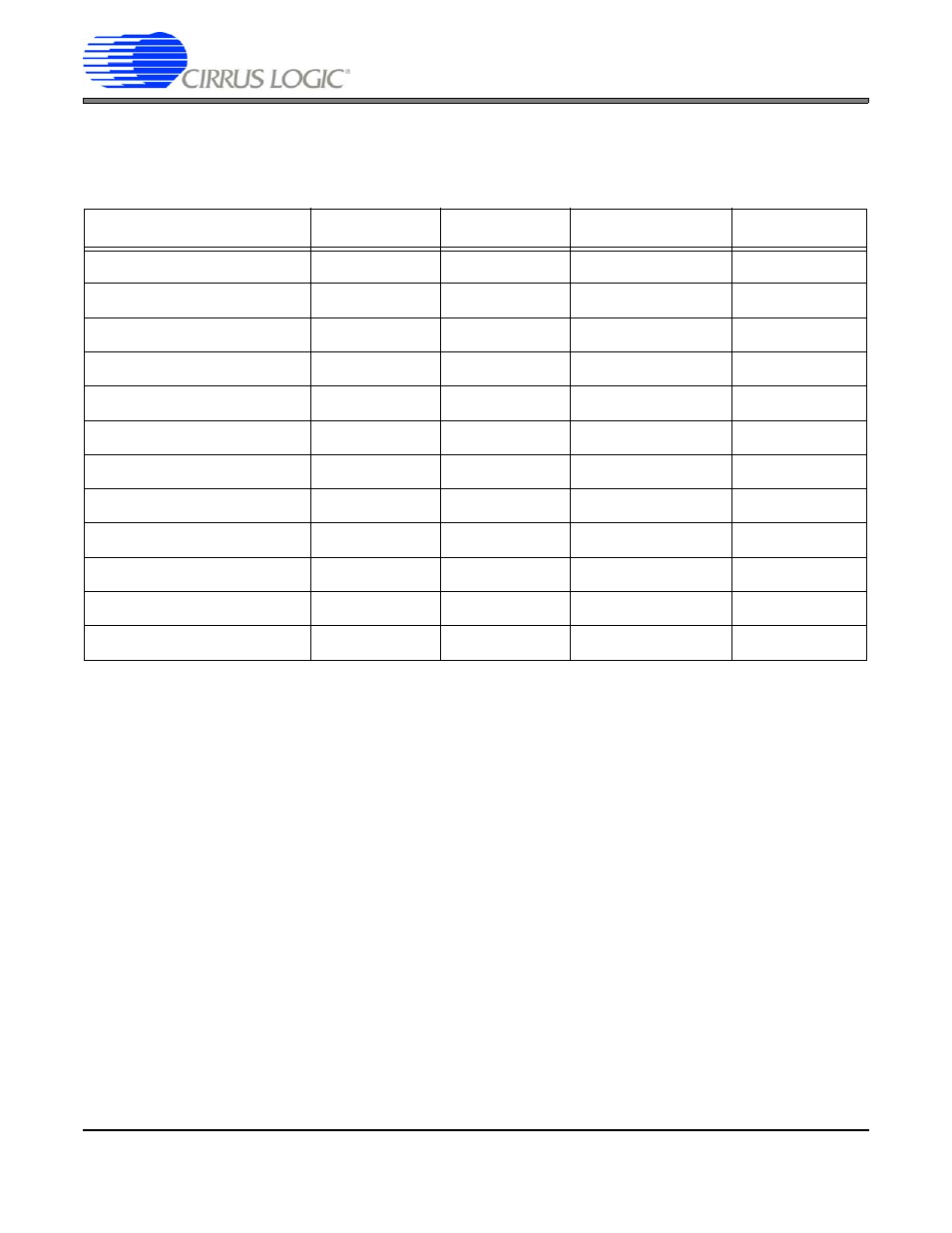

Appendix A: Example HSYNC/VSYNC-Style LCD Display - LG/Philips’s LB064V02-B1

The display used in this example is an LG/Philips LB064V02-B1. Relevant specifications taken from the datasheet

are as follows:

The first step in setting up the EP93xx raster engine for this display involves determining the proper

SPCLK rate. Using the equations from section

“Setting Up Display Timing” on page 16

:

tHORIZ = tHACTIVE + tHFRONTPORCH + tHSYNC + tHBACKPORCH

tHORIZ = 640 + 24 + 96 + 40 = 800 (SPCLK periods)

tVERT = tVACTIVE + tVFRONTPORCH + tVSYNC + tVBACKPORCH

tVERT = 480 + 10 + 2 + 33 = 525 (HSYNC pulses)

fVSYNC = 60 Hz

VIDCLK = tHORIZ * tVERT * fVSYNC

VIDCLK = 800 * 525 * 60 = 25200000 SPCLK periods per second (25.2 MHz)

Now that the VIDCLK rate is known, the source of that clock must be determined. This is done using the algorithm

shown in

For this example we will use the actual frequency (not 2x the frequency) and the possible PDIV

Item

MIN

TYP

MAX

UNIT

DCLK Frequency

22

25

28

MHz

Hsync Width

24

96

144

DCLK pulses

Vsync Width

2

2

-

Hsync pulses

Vsync Frequency

55

60

65

Hz

Horizontal Valid

640

640

640

DCLK pulses

Horizontal Back Porch

16

40

-

DCLK pulses

Horizontal Front Porch

16

24

-

DCLK pulses

Horizontal Blank

56

160

(non-active area)

DCLK pulses

Vertical Valid

480

480

480

Hsync pulses

Vertical Back Porch

2

33

-

Hsync pulses

Vertical Front Porch

2

10

-

Hsync pulses

Vertical Blank

6

45

(non active area)

Hsync pulses

Table 14. LB064V02-B1 Specifications