An269 – Cirrus Logic AN269 User Manual

Page 49

AN269

AN269REV1

49

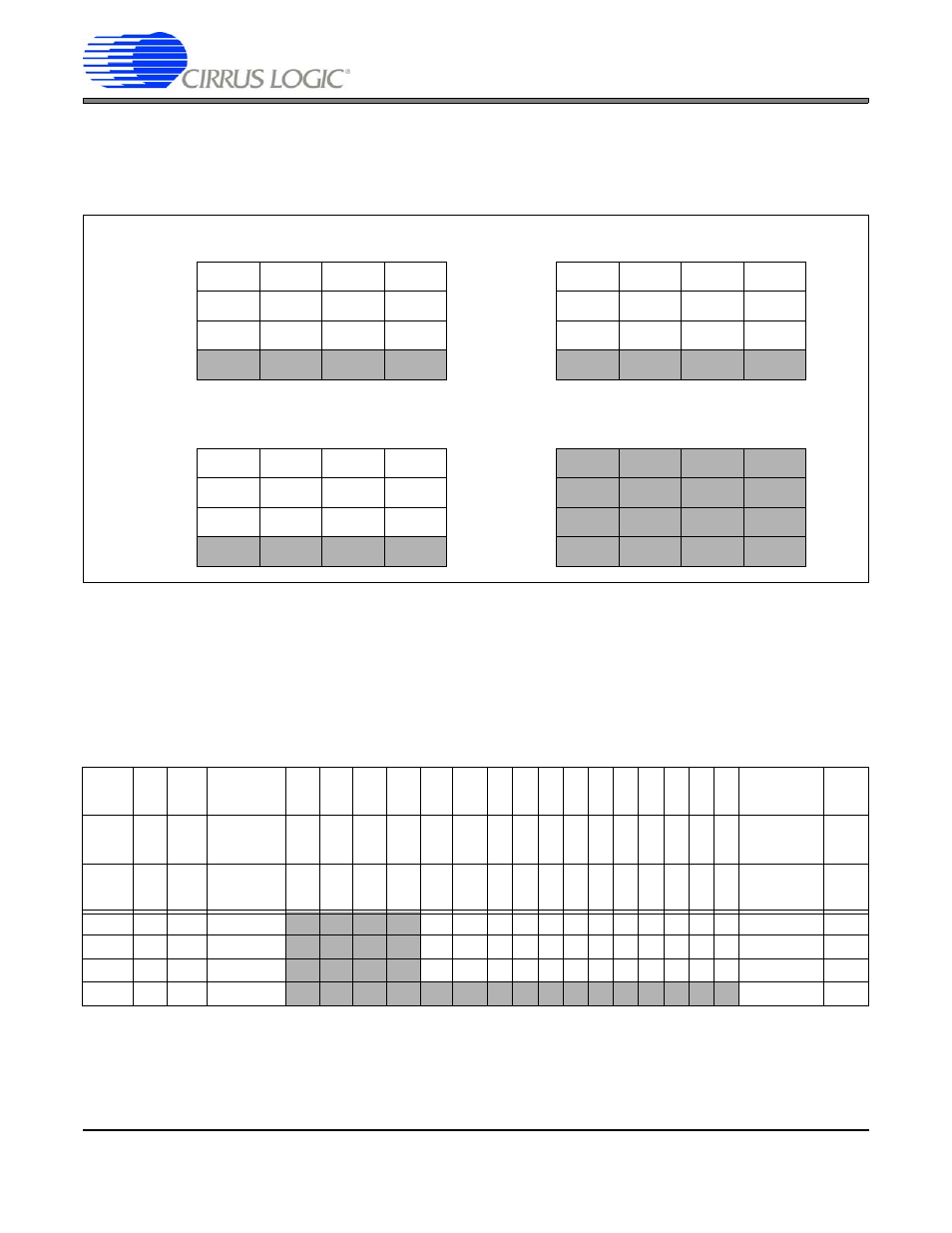

To edit the entries in the grayscale LUT, the first step is to create the pixel pattern for each frame. As noted

in the EP93xx User’s Guide, there can be 3 or 4 horizontal pixels, 3 or 4 vertical pixels, and 3 or 4 video

frames in the pattern.

As an example, take the frame pattern shown in

In the example above, the pattern uses 4 columns, 3 rows, and 3 frames. The areas shaded in gray are not

used in this example, and therefore bits D18=D17=0 and D16=1 for this pattern. Now an input pixel value

that will generate this pattern should be chosen. This can be any of the 8 available input values except 000b

and 111b, which will always generate a 0 or 1 output, respectively. For this example, assume an entry of

010b.

For an input pixel value of 010b, the relevant entries in the grayscale LUT are base+0x08, base+0x28,

base+0x48, and base+0x68. This yields the table (by transposing values from

) shown below.

Frame 0

HCNT

=00b

HCNT

=01b

HCNT

=10b

HCNT

=11b

Frame 1

HCNT

=00b

HCNT

=01b

HCNT

=10b

HCNT

=11b

VCNT=00b

1

0

1

1

VCNT=00b

1

1

1

0

VCNT=01b

1

1

0

1

VCNT=01b

0

1

1

1

VCNT=10b

1

1

1

0

VCNT=10b

1

0

1

1

VCNT=11b

X

X

X

X

VCNT=11b

X

X

X

X

Frame 2

HCNT

=00b

HCNT

=01b

HCNT

=10b

HCNT

=11b

Frame 3

HCNT

=00b

HCNT

=01b

HCNT

=10b

HCNT

=11b

VCNT=00b

1

1

0

1

VCNT=00b

X

X

X

X

VCNT=01b

1

0

1

1

VCNT=01b

X

X

X

X

VCNT=10b

0

1

1

1

VCNT=10b

X

X

X

X

VCNT=11b

X

X

X

X

VCNT=11b

X

X

X

X

Table 12. Example Grayscale pattern generation

Frame Vert Horz

VCNT

(lines)

11

11

11

11

10

10

10 10 01 01 01 01 00 00 00 00

GrySclLUT

Address *4

Ctr

Ctr

Ctr

HCNT

(pixels)

11

10

01

00

11

10

01 00 11 10 01 00 11 10 01 00

Frame

Pixel

D18

D17 D16

register

address

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Value

0

0

1

base + 0x08

0

0

0

0

0

0

1

0

1

1

0

0

0

0

0

1

00

010

0

0

1

base + 0x28

0

0

0

0

1

1

0

0

0

0

1

0

0

0

1

0

01

010

0

0

1

base + 0x48

0

0

0

0

0

0

0

1

1

0

0

1

1

1

0

0

10

010

0

0

1

base + 0x68

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

11

010

Table 13. Example Entries for Sample Pattern