An269 – Cirrus Logic AN269 User Manual

Page 56

56

AN269REV1

AN269

Appendix B:Example Frame Type 1 Display - Kyocera’s KCS057QV1AJ-G20

For this section, we will be using the Kyocera KCS057QV1AJ-G20 3-color STN display. The relevant timing speci-

fications from the datasheet are shown in

.

Other relevant information from the Kyocera datasheet includes the horizontal and vertical resolution, which is

320x240, and the ideal refresh rate, which is 73 Hz (taken from the “Frame Frequency”). Since the display operates

in 2-2/3 pixel mode, there will be 1 VIDCLK/Pixel.

The first step in figuring the timings is to determine the VIDCLK rate using the following formula:

DesiredVidClkFreq = {[(VIDCLKs/Pixel) * (Horizontal Resolution)] + [(2 SPCLKs for each region)*(4 regions)]} *

(Vertical Resolution) * (Desired Refresh Rate)

DesiredVidClkFreq = {[(1 VIDCLK/Pixel) * (320 Pixels)] + [(2 SPCLKs for each region)*(4 regions)]} * (240 Pixels) *

(73 Hz) = (320 + 8)*(240)*(73) = 5746560 Hz

Note that this is a first estimate of the VIDCLK rate, and may need to be increased to meet timing specifications on

the part.

Next, the VIDCLKDIV register should be set up to deliver a 5746560-Hz VIDCLK. This is done using the algorithm

shown in the section

“Generation of the Video Clock, VIDCLK” on page 2

. Using this yields a VIDCLK of just over

5.8 MHz

The VidClkPeriod is the period of the actual VIDCLK rate:

VidClkPeriod = 1 / ActualVidClkFreq = 1 / 5.8 MHz = 172 ns

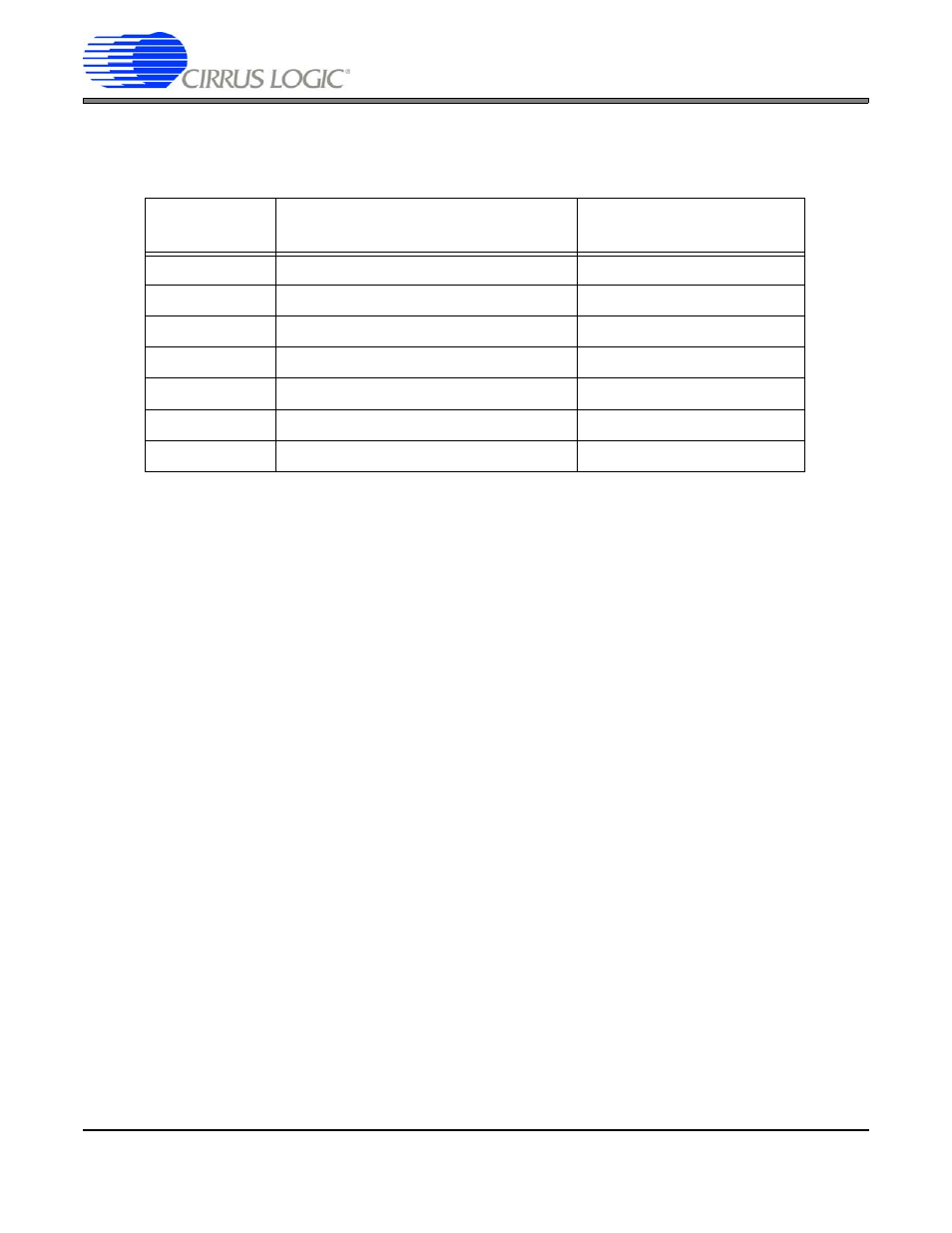

Timing

Parameter

Kyocera Datasheet Symbol

Value

tHSYNCH

tWLPH

50 ns

tHSYNCL

tWLPL

370 ns

tHSYNCSPCLK

tLC

120-tWLPH (min 70 ns)

tSPCLKHSYNC

tCL

0

tSPCLK

tHVCSYNC

tFS

100 ns

tVCHSYNC

tFH

30 ns

Table 17. Kyocera Display Timings