An269 – Cirrus Logic AN269 User Manual

Page 53

AN269

AN269REV1

53

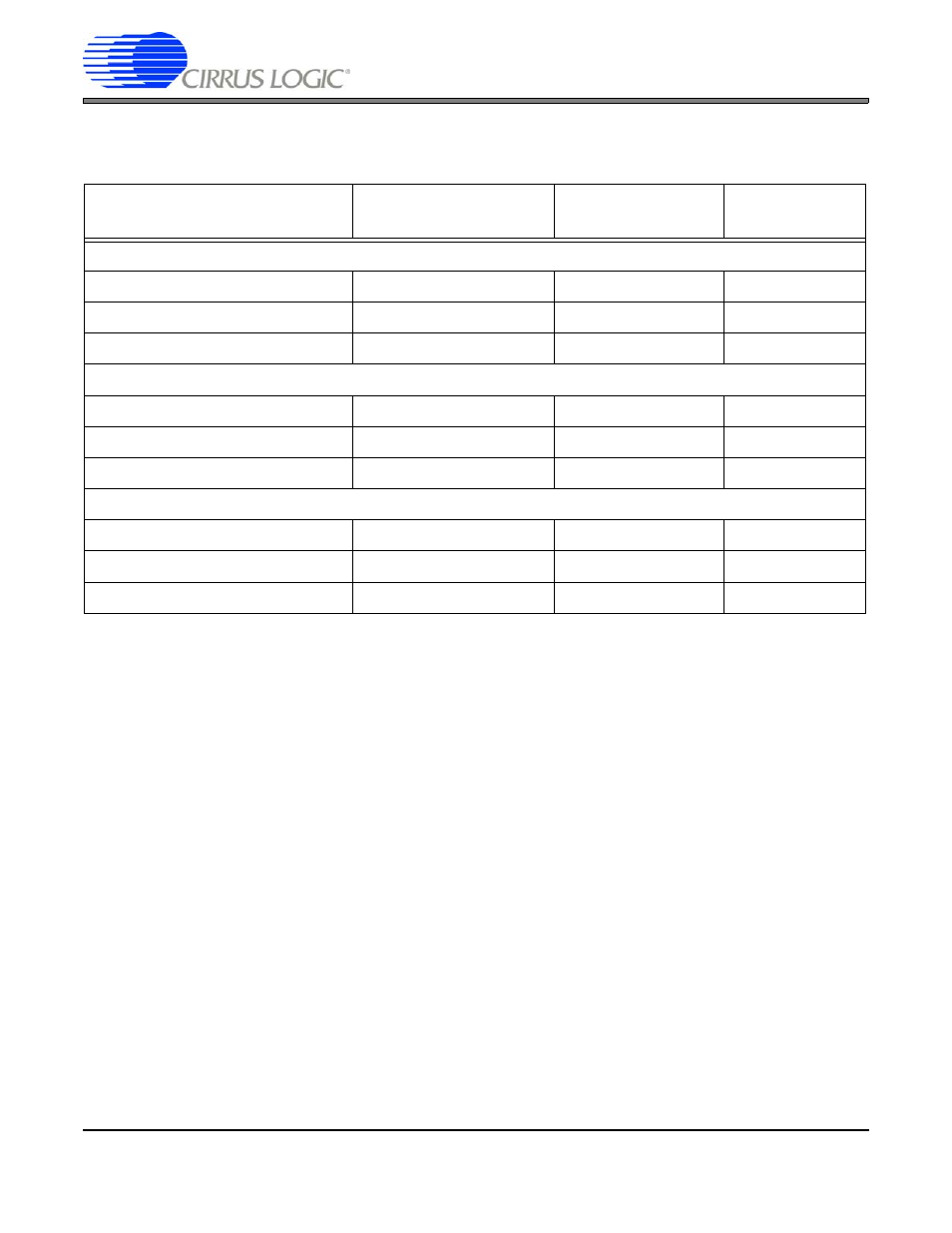

values of 2, 2.5, and 3. This yields possible values of VDIV. Using those values as PDIV and VDIV, we can compute

the error in VIDCLK by subtracting the desired value of SPCLK (25.2 MHz). Assuming an external clock rate of

14.745600 MHz, PLL1 = 400 MHz, PLL2 = 384 MHz, we come up with the following table of values:

Next, the Horizontal Synchronization Signals can be determined, using the equations in

HClkTotal = tHORIZ – 1

HClkTotal = 800 – 1 = 799 (VIDCLK periods)

therefore:

HSyncStart = HClkTotal

HSyncStart = 799

HSyncStop = HClkTotal – tHSYNC

HSyncStop = 799 – 96 = 703

HBlankStart = HClkTotal - tHSYNC - tHBACKPORCH - 1

HBlankStart = 799 - 96 - 40 - 1 = 662

HBlankStop = tHFRONTPORCH - 1

HBlankStop = 23 - 1 = 22

HActiveStart = HBlankStart

HActiveStart = 662

Input Frequency and Source = fIN

VDIV = fIN /

(PDIV*SPCLK)

Actual SPCLK Rate

= fIN / (PDIV*VDIV)

Error

External Clock = 14.7456 MHz

PDIV = 2

0

N/A[foot]

PDIV = 2.5

0

N/A[foot]

PDIV = 3

0

N/A[foot]

PLL1 = 400 MHz

PDIV = 2

8

25.0 MHz

0.2 MHz

PDIV = 2.5

6

26.7 MHz

1.5 MHz

PDIV = 3

5

26.7 MHz

1.5 MHz

PLL2 = 384 MHz

PDIV = 2

8

24.0 MHz

PDIV = 2.5

6

25.6 MHz

PDIV = 3

5

25.6 MHz

Table 15. Determination of VIDCLK source