2 horizontal alignment signals, Figure 10, An269 – Cirrus Logic AN269 User Manual

Page 19

AN269

AN269REV1

19

6.1.2

Horizontal Alignment Signals

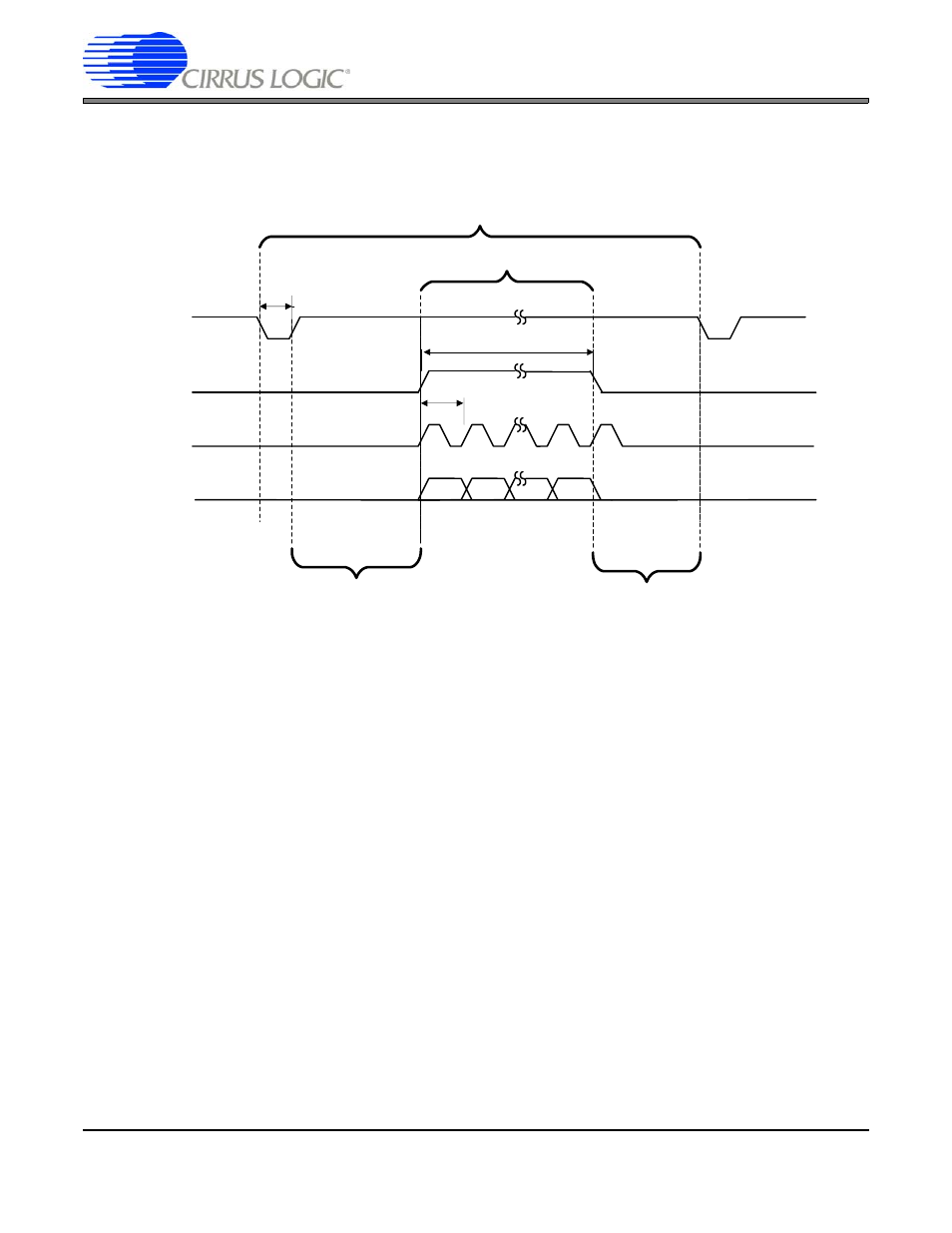

Timings for a single horizontal line can be seen in

. To determine when these signals become

active, the horizontal frame timing registers HClkTotal, HSyncStrtStop, HActiveStrtStop, HBlankStrtStop

and HClkStrtStop must be set.

“Using the Horizontal and Vertical Counter for Timing-Signal Generation” on page 4

for a description of

the horizontal timing registers.

Recall that the timing specifications for this type of display interface will list an HSYNC Width, Horizontal

Back Porch Width, Horizontal Front Porch Width, Horizontal Valid, and Horizontal Blank lengths.

The HClkTotal register will hold the total length of a single line measured in VIDCLK periods.The equation

for this is shown here:

HClkTotal = tHORIZ – 1

Note that 1 is subtracted for the total as this is a 0-based counter implementation. Also, remember all mea-

surements are assumed to be in periods of VIDCLK. All other signals are determined using this as a time

base.

To determine when the HSYNC, SPCLK (via HCLKEN), and BLANK (via HBLANK) signals should be-

come active during a horizontal line, it is easiest to draw them out as shown in

. This diagram

shows the line counter along the bottom, starting at HClkTotal and counting down to 0. Each line starts

with the counter set to HClkTotal. It then decrements by 1 for each VIDCLK clock period, regardless of

whether SPCLK is present or not. When the counter reaches 0, it is reset to HClkTotal.

HSYNC

SPCLK

BLANK

t

HACTIVE

t

HSYNC

t

DCLK

Single Horizontal Line

DATA

Back Porch Interval t

HBACKPORCH

Front Porch Interval t

HFRONTPORCH

Active Video

Figure 10. Typical Horizontal Line for HSYNC/VSYNC Display