Cirrus Logic CS53L30 User Manual

Cs53l30, Analog input and adc features, Digital processing features

Table of contents

Document Outline

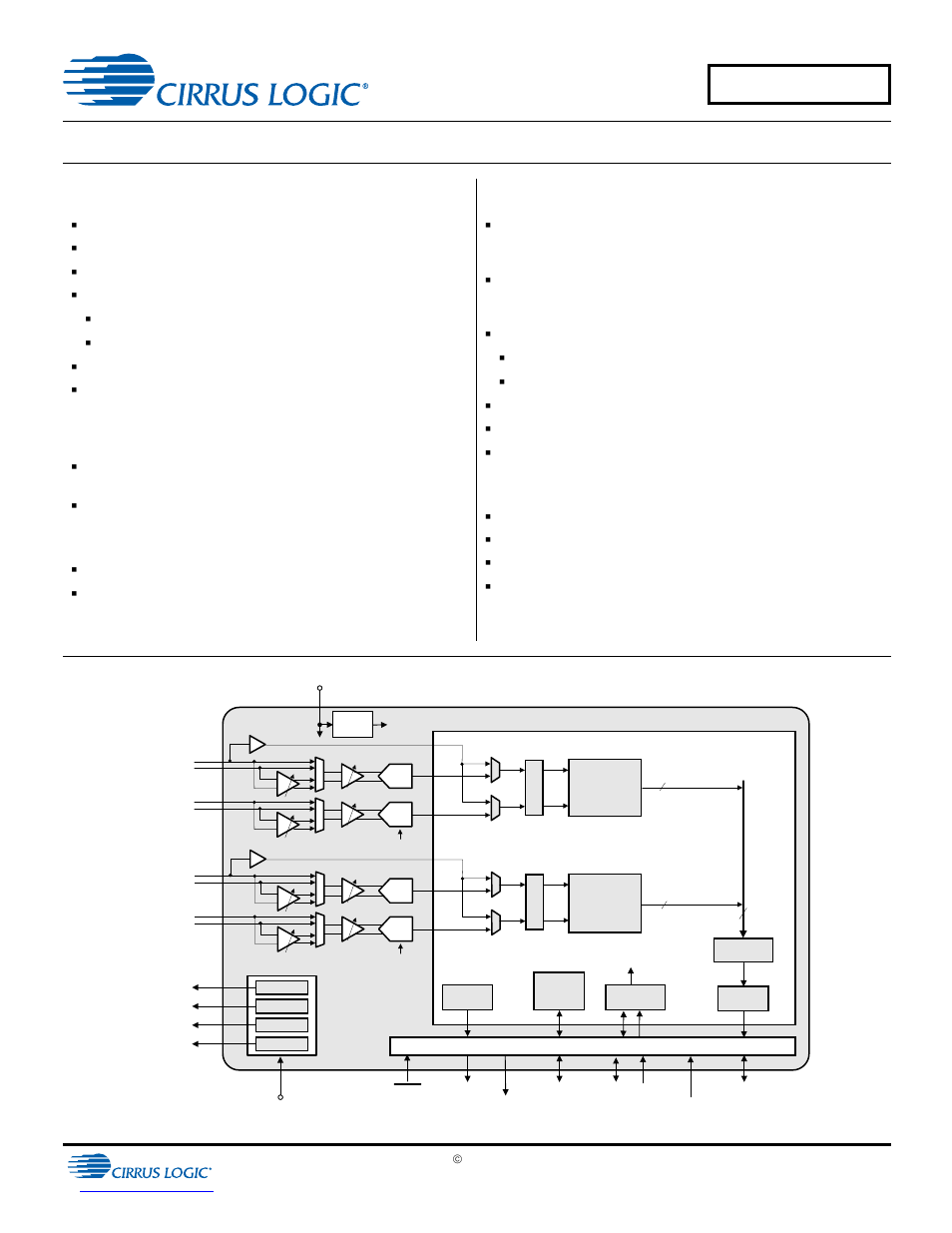

- Low-Power Quad-Channel Microphone ADC with TDM Output

- 1 Pin Descriptions

- 2 Typical Connection Diagram

- 3 Characteristics and Specifications

- Table 3-1. Recommended Operating Conditions

- Table 3-2. Absolute Maximum Ratings

- Table 3-3. Combined ADC On-Chip Analog, Digital Filter, SRC, and DMIC Characteristics

- Table 3-4. ADC High-Pass Filter (HPF) Characteristics

- Table 3-5. Analog-Input-to-Serial-Port Characteristics

- Table 3-6. MIC BIAS Characteristics

- Table 3-7. Power-Supply Rejection Ratio (PSRR) Characteristics

- Table 3-8. Power Consumption

- Table 3-10. Switching Specifications—Digital Mic Interface

- Table 3-11. Specifications—I2S

- Table 3-12. Switching Specifications—Time-Division Multiplexed (TDM) Mode

- Table 3-13. Switching Specifications—I2C Control Port

- Table 3-14. Digital Interface Specifications and Characteristics

- Table 3-15. Thermal Overload Detection Characteristics

- 4 Functional Description

- 4.1 Overview

- 4.2 Resets

- 4.3 Interrupts

- 4.4 Capture-Path Inputs

- 4.5 Digital Microphone (DMIC) Interface

- 4.6 Serial Ports

- 4.7 TDM Mode

- 4.8 Synchronous Sample-Rate Converter (SRC)

- 4.9 Multichip Synchronization Protocol

- 4.10 Input Path Source Selection and Powering

- 4.11 Thermal Overload Notification

- 4.12 MUTE Pin

- 4.13 Power-Up and Power-Down Control

- 4.14 I2C Control Port

- 4.15 QFN Thermal Pad

- 5 Systems Applications

- 6 Register Quick Reference

- 7 Register Descriptions

- 7.1 Device ID A and B

- 7.2 Device ID C and D

- 7.3 Device ID E

- 7.4 Revision ID

- 7.5 Power Control

- 7.6 MCLK Control

- 7.7 Internal Sample Rate Control

- 7.8 Mic Bias Control

- 7.9 ASP Configuration Control

- 7.10 ASP Control 1

- 7.11 ASP TDM TX Control 1–4

- 7.12 ASP TDM TX Enable 1–6

- 7.13 ASP Control 2

- 7.14 Soft Ramp Control

- 7.15 LRCK Control 1

- 7.16 LRCK Control 2

- 7.17 MUTE Pin Control 1

- 7.18 MUTE Pin Control 2

- 7.19 Input Bias Control 1

- 7.20 Input Bias Control 2

- 7.21 DMIC1 Stereo Control

- 7.22 DMIC2 Stereo Control

- 7.23 ADC1/DMIC1 Control 1

- 7.24 ADC1/DMIC1 Control 2

- 7.25 ADC1 Control 3

- 7.26 ADC1 Noise Gate Control

- 7.27 ADC1A/1B AFE Control

- 7.28 ADC1A/1B Digital Volume

- 7.29 ADC2/DMIC2 Control 1

- 7.30 ADC2/DMIC2 Control 2

- 7.31 ADC2 Control 3

- 7.32 ADC2 Noise Gate Control

- 7.33 ADC2A/2B AFE Control

- 7.34 ADC2A/2B Digital Volume

- 7.35 Device Interrupt Mask

- 7.36 Device Interrupt Status

- 8 Parameter Definitions

- 9 Plots

- 10 Package Dimensions

- 11 Thermal Characteristics

- 12 Ordering Information

- 13 Revision History