15 lrck control 1, 16 lrck control 2, 17 mute pin control 1 – Cirrus Logic CS53L30 User Manual

Page 51: 18 mute pin control 2, 15 lrck control 1 7.16 lrck control 2 7.17 mute, 18 mute, Lrck_tpwh[10:3, Lrck_tpwh[2:0, P. 51, Lrck_50_npw

DS992F1

51

CS53L30

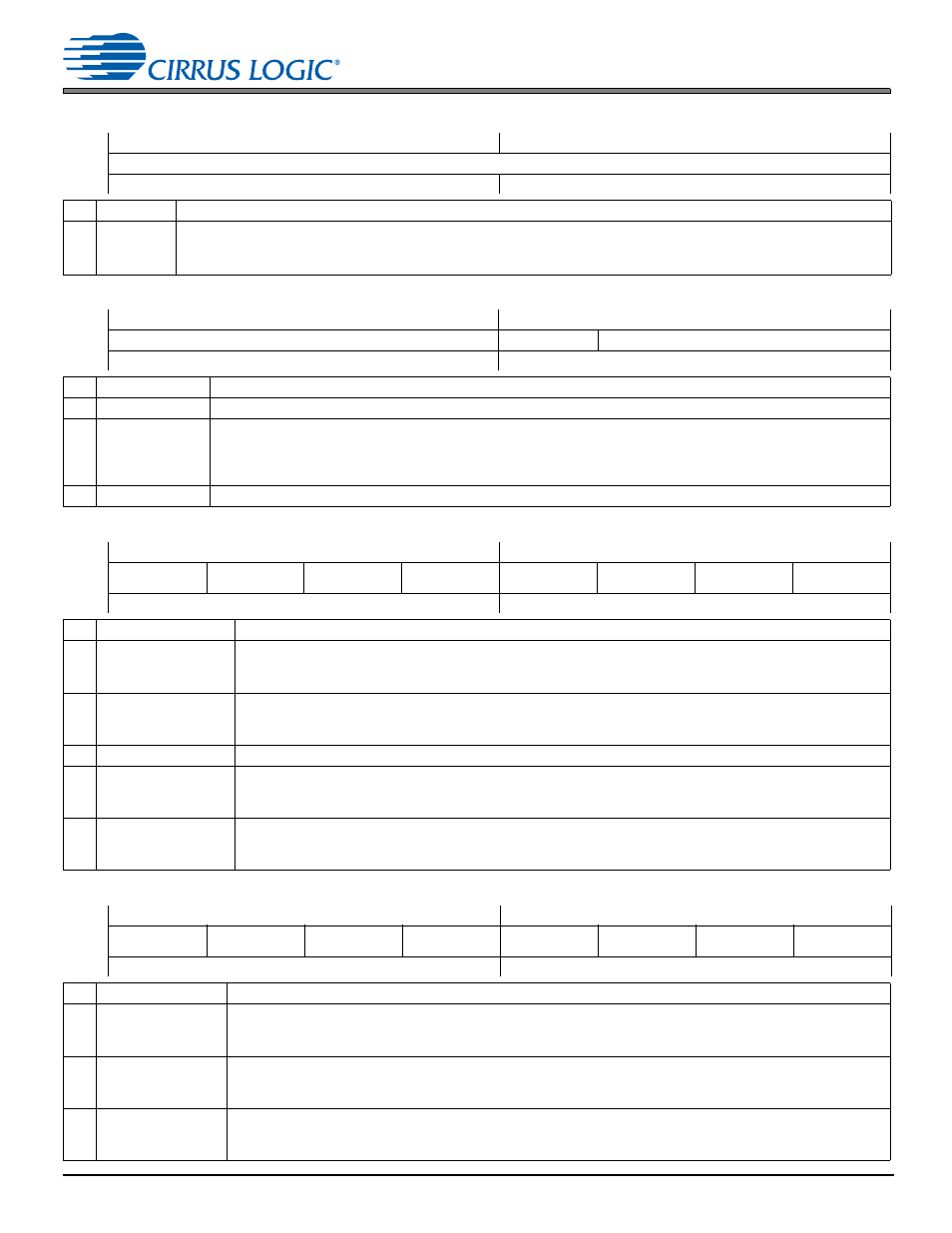

7.15 LRCK Control 1

7.15 LRCK Control 1

Address 0x1B

R/W

7

6

5

4

3

2

1

0

LRCK_TPWH[10:3]

Default

0

0

0

0

0

0

0

0

Bits

Name

Description

7:0

LRCK_

TPWH[10:3]

LRCK high-time pulse width [10:3]. With LRCK_TPWH[2:0], sets the number of SCLK cycles for which the LRCK remains

high. Active only when in TDM Mode and LRCK_50_NPW = 1.

0x000 (Default) LRCK high time is 1 SCLK wide

0x001 LRCK high time is 2 SCLKs wide

7.16 LRCK Control 2

Address 0x1C

R/W

7

6

5

4

3

2

1

0

—

LRCK_50_NPW

LRCK_TPWH[2:0]

Default

0

0

0

0

0

0

0

0

Bits

Name

Description

7:4

—

Reserved

3

LRCK_50_NPW

LRCK either 50% duty cycle or programmable high-time pulse width. In TDM Mode, pulse width can be 50% or

programmable up to 2047 x SCLK cycles.

0 (Default) High-time pulse width set by LRCK_TPWH[10:0].

1 50% duty cycle

2:0 LRCK_TPWH[2:0] LRCK high time pulse width [2:0]. With LRCK_TPWH[10:3], sets the LRCK high time in TDM Mode. See

.

7.17 MUTE Pin Control 1

Address 0x1F

R/W

7

6

5

4

3

2

1

0

MUTE_PDN_

ULP

MUTE_PDN_

LP

—

MUTE_M4B_

PDN

MUTE_M3B_

PDN

MUTE_M2B_

PDN

MUTE_M1B_

PDN

MUTE_MB_

ALL_PDN

Default

0

0

0

0

0

0

0

0

Bits

Name

Description

7

MUTE_PDN_ULP

Power down all ADCs, references, and mic biases when the MUTE pin is asserted.

0 (Default) Not affected by MUTE pin

1 Powered down when MUTE pin asserted

6

MUTE_PDN_LP

Power down all ADCs and mic biases when the MUTE pin is asserted.

0 (Default) Not affected by MUTE pin

1 Powered down when MUTE pin asserted

5

—

Reserved

4, 3,

2, 1

MUTE_MxB_PDN

Individual power down controls for the MICx biases when the MUTE pin is asserted.

0 (Default) Not affected by MUTE pin

1 Powered down when MUTE pin asserted

0

MUTE_MB_ALL_PDN Power down all mic biases when the MUTE pin is asserted.

0 (Default) Not affected by MUTE pin

1 Powered down when MUTE pin asserted

7.18 MUTE Pin Control 2

Address 0x20

R/W

7

6

5

4

3

2

1

0

MUTE_PIN_

POLARITY

MUTE_ASP_

TDM_PDN

MUTE_ASP_

SDOUT2_PDN

MUTE_ASP_

SDOUT1_PDN

MUTE_

ADC2B_PDN

MUTE_

ADC2A_PDN

MUTE_

ADC1B_PDN

MUTE_

ADC1A_PDN

Default

1

0

0

0

0

0

0

0

Bits

Name

Description

7

MUTE_PIN_

POLARITY

MUTE pin polarity.

0 MUTE pin is active low.

1 (Default) MUTE pin is active high.

6

MUTE_ASP_TDM_

PDN

Power down TDM when MUTE pin is asserted.

0 (Default) Not affected by MUTE pin.

1 If MUTE_ASP_SDOUT1_PDN is set, the TDM interface is powered down when MUTE pin is asserted.

5

MUTE_ASP_

SDOUT2_PDN

Power down ASP_SDOUT2 when MUTE pin is asserted. Setting is ignored in TDM Mode.

0 (Default) Not affected by MUTE pin.

1 Powered down when MUTE pin asserted.