32 adc2 noise gate control, 33 adc2a/2b afe control, 34 adc2a/2b digital volume – Cirrus Logic CS53L30 User Manual

Page 56: A_pr, Mp[1, A_pga, B_pr, B_pga, Adc2x_vol, Adc2x_pga_vol

56

DS992F1

CS53L30

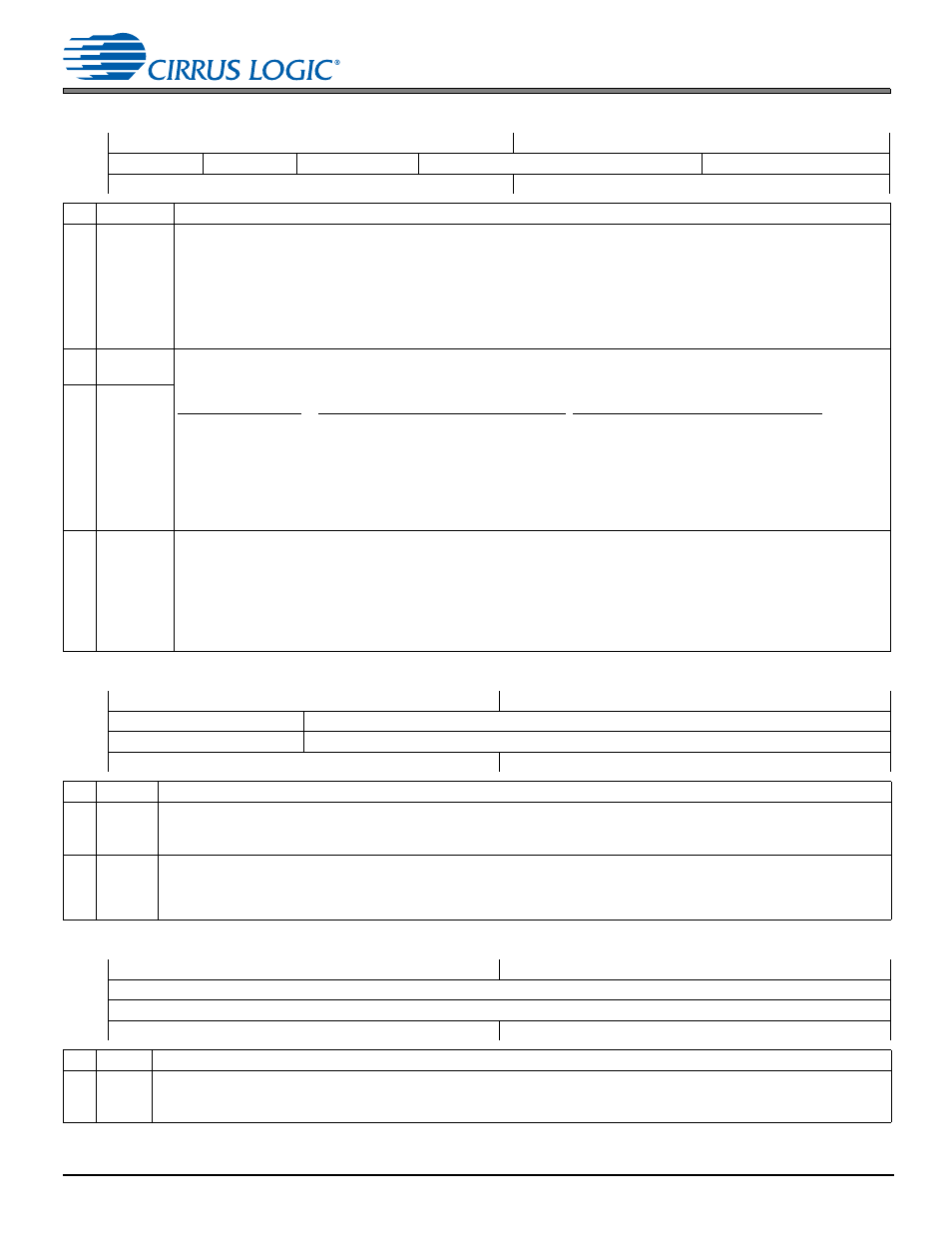

7.32 ADC2 Noise Gate Control

7.32 ADC2 Noise Gate Control

Address 0x30

R/W

7

6

5

4

3

2

1

0

ADC2B_NG

ADC2A_NG

ADC2_NG_BOOST

ADC2_NG_THRESH[2:0]

ADC2_NG_DELAY[1:0]

Default

0

0

0

0

0

0

0

0

Bits

Name

Description

7,6 ADC2x_NG ADC2 noise-gate enable for Channels A and B. Enables independent noise gating for Channels A and B if ADC1_NG_

ALL = 0. This bit has no effect if ADC1_NG_ALL = 1

0 (Default) Disable noise gating on Channel x

1 Enable noise gating on Channel x. If a channel’s signal amplitude remains below the threshold setting (refer to ADC2_

NG_THRESH) for longer than the attack delay (debounce) time (refer to ADC2_NG_DELAY), noise gate muting is

applied to only that channel.

• Noise gate muting is removed (released) without debouncing when the signal level exceeds the threshold.

• Noise gate attack and release rates (soft-ramped as a function of Fs or abrupt) are set according to

.

5

ADC2_NG_

BOOST

ADC2 noise-gate threshold and boost for Channels A and B. These fields define the signal level where the noise gate begins

to engage. For low settings, the noise gate may not fully engage until the signal level is a few dB lower. Sets threshold level

(±2 dB) for Channel A and B noise gates. ADC2_NG_BOOST configures a +30-dB boost to the threshold setting.

4:2 ADC2_NG_

THRESH

ADC2_NG_THRESH

000

001

010

011

100

101

110

111

Minimum Setting (ADC2_NG_BOOST = 0)

(Default) –64 dB

–66 dB

–70 dB

–73 dB

–76 dB

–82 dB

Reserved

Reserved

Minimum Setting (ADC2_NG_BOOST = 1)

–34 dB

–36 dB

–40 dB

–43 dB

–46 dB

–52 dB

–58 dB

–64 dB

1:0 ADC2_NG_

DELAY

Noise-gate delay timing for ADC2 Channels A and B. Sets the delay (debounce) time before the noise gate mute attacks.

00 (Default) 50 * (time base) ms

01 100 * (time base) ms

10 150 * (time base) ms

11 200 * (time base) ms

Time base = (6144 x [MCLK

INT

scaling factor])/MCLK

INT

.

MCLK

INT

scaling factor is 1, 2, or 4, depending on FS

INT

and the MCLK_INT_SCALE setting.

lists supported

configurations and their corresponding MCLK

INT

scaling factors. For MCLK

INT

= 6.144 MHz and MCLK_INT_SCALE = 0,

time base is 1 ms.

7.33 ADC2A/2B AFE Control

Address 0x31–0x32

R/W

7

6

5

4

3

2

1

0

ADC2A_PREAMP[1:0]

ADC2A_PGA_VOL[5:0]

ADC2B_PREAMP[1:0]

ADC2B_PGA_VOL[5:0]

Default

0

0

0

0

0

0

0

0

Bits

Name

Description

7:6

ADC2x_

PREAMP

ADC2x mic preamp gain. Sets the gain of the mic preamp.

00 (Default) 0 dB (preamp bypassed)

01 +10 dB

10 +20 dB

11 Reserved

5:0

ADC2x_

PGA_

VOL

ADC2x PGA volume. Sets PGA attenuation/gain. Step size: ~0.5 dB.

01 1111–01 1000 12 dB…

00 0001 +0.5 dB

00 0000 (Default) 0 dB

11 1111 –0.5 dB

11 1010 –3.0 dB (Target setting for 600-mVrms analog-input amplitude)…

11 0100–10 0000 –6.0 dB

7.34 ADC2A/2B Digital Volume

Address 0x33–0x34

R/W

7

6

5

4

3

2

1

0

ADC2A_VOL[7:0]

ADC2B_VOL[7:0]

Default

0

0

0

0

0

0

0

0

Bits

Name

Description

7:0 ADC2x_

VOL

ADC2x digital volume. Sets the ADC2x or DMIC signal volume based on the input source (see

). Step size: 1.0 dB.

0111 1111–0000 1100 +12 dB

0000 1011 +11 dB …

0000 0000(Default) 0 dB

1111 1111 –1.0 dB

1111 1110 –2.0 dB…

1010 0000 –96.0 dB

1001 1111 –1000 0000 Mute