Cs53l30, 6 register quick reference – Cirrus Logic CS53L30 User Manual

Page 46

46

DS992F1

CS53L30

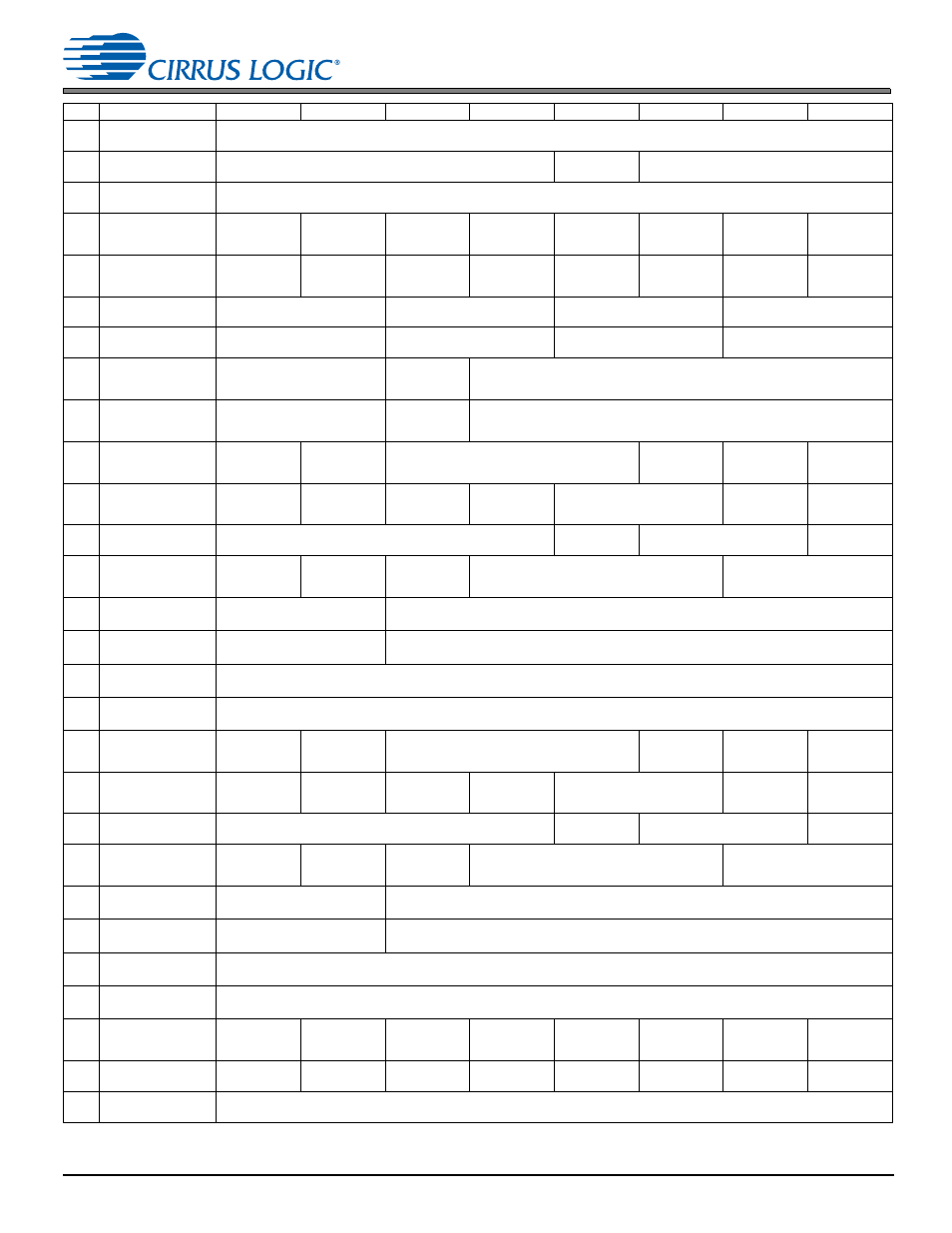

6 Register Quick Reference

0x1B LRCK Control 1

LRCK_TPWH[10:3]

0

0

0

0

0

0

0

0

0x1C LRCK Control 2

—

LRCK_50_NPW

LRCK_TPWH[2:0]

0

0

0

0

0

0

0

0

0x1D–

0x1E

Reserved

—

0

0

0

0

0

0

0

0

0x1F MUTE Pin Control 1

MUTE_PDN_

ULP

MUTE_PDN_LP

—

MUTE_M4B_

PDN

MUTE_M3B_

PDN

MUTE_M2B_

PDN

MUTE_M1B_

PDN

MUTE_MB_

ALL_PDN

0

0

0

0

0

0

0

0

0x20 MUTE Pin Control 2

MUTE_PIN_

POLARITY

MUTE_ASP_

TDM_PDN

MUTE_ASP_

SDOUT2_PDN

MUTE_ASP_

SDOUT1_PDN

MUTE_ADC2B_

PDN

MUTE_ADC2A_

PDN

MUTE_ADC1B_

PDN

MUTE_ADC1A_

PDN

1

0

0

0

0

0

0

0

0x21 Input Bias Control 1

IN4M_BIAS[1:0]

IN4P_BIAS[1:0]

IN3M_BIAS[1:0]

IN3P_BIAS[1:0]

1

0

1

0

1

0

1

0

0x22 Input Bias Control 2

IN2M_BIAS[1:0]

IN2P_BIAS[1:0]

IN1M_BIAS[1:0]

IN1P_BIAS[1:0]

1

0

1

0

1

0

1

0

0x23 DMIC1 Stereo Control

—

DMIC1_

STEREO_ENB

—

1

0

1

0

1

0

0

0

0x24 DMIC2 Stereo Control

—

DMIC2_

STEREO_ENB

—

1

1

1

0

1

1

0

0

0x25 ADC1/DMIC1 Control 1

ADC1B_PDN

ADC1A_PDN

—

DMIC1_PDN

DMIC1_SCLK_

DIV

CH_TYPE

0

0

0

0

0

1

0

0

0x26 ADC1/DMIC1 Control 2 ADC1_NOTCH_

DIS

—

ADC1B_INV

ADC1A_INV

—

ADC1B_DIG_

BOOST

ADC1A_DIG_

BOOST

0

0

0

0

0

0

0

0

0x27 ADC1 Control 3

—

ADC1_HPF_EN

ADC1_HPF_CF[1:0]

ADC1_NG_ALL

0

0

0

0

1

0

0

0

0x28 ADC1 Noise Gate

ADC1B_NG

ADC1A_NG

ADC1_NG_

BOOST

ADC1_NG_THRESH[2:0]

ADC1_NG_DELAY[1:0]

0

0

0

0

0

0

0

0

0x29 ADC1A AFE Control

ADC1A_PREAMP[1:0]

ADC1A_PGA_VOL[5:0]

0

0

0

0

0

0

0

0

0x2A ADC1B AFE Control

ADC1B_PREAMP[1:0]

ADC1B_PGA_VOL[5:0]

0

0

0

0

0

0

0

0

0x2B ADC1A Digital Volume

ADC1A_VOL[7:0]

0

0

0

0

0

0

0

0

0x2C ADC1B Digital Volume

ADC1B_VOL[7:0]

0

0

0

0

0

0

0

0

0x2D ADC2/DMIC2 Control 1

ADC2B_PDN

ADC2A_PDN

—

DMIC2_PDN

DMIC2_SCLK_

DIV

—

0

0

0

0

0

1

0

0

0x2E ADC2/DMIC2 Control 2 ADC2_NOTCH_

DIS

—

ADC2B_INV

ADC2A_INV

—

ADC2B_DIG_

BOOST

ADC2A_DIG_

BOOST

0

0

0

0

0

0

0

0

0x2F ADC2 Control 3

—

ADC2_HPF_EN

ADC2_HPF_CF[1:0]

ADC2_NG_ALL

0

0

0

0

1

0

0

0

0x30 ADC2 Noise Gate

ADC2B_NG

ADC2A_NG

ADC2_NG_

BOOST

ADC2_NG_THRESH[2:0]

ADC2_NG_DELAY[1:0]

0

0

0

0

0

0

0

0

0x31 ADC2A AFE Control

ADC2A_PREAMP[1:0]

ADC2A_PGA_VOL[5:0]

0

0

0

0

0

0

0

0

0x32 ADC2B AFE Control

ADC2B_PREAMP[1:0]

ADC2B_PGA_VOL[5:0]

0

0

0

0

0

0

0

0

0x33 ADC2A Digital Volume

ADC2A_VOL[7:0]

0

0

0

0

0

0

0

0

0x34 ADC2B Digital Volume

ADC2B_VOL[7:0]

0

0

0

0

0

0

0

0

M_PDN_DONE M_THMS_TRIP

M_SYNC_

DONE

M_ADC2B_

OVFL

M_ADC2A_

OVFL

M_ADC1B_

OVFL

M_ADC1A_

OVFL

M_MUTE_PIN

1

1

1

1

1

1

1

1

(Read Only)

PDN_DONE

THMS_TRIP

SYNC_DONE

ADC2B_OVFL

ADC2A_OVFL

ADC1B_OVFL

ADC1A_OVFL

MUTE_PIN

x

x

x

x

x

x

x

x

0x37–

0x7F

Reserved

—

0

0

0

0

0

0

0

0

Adr.

Function

7

6

5

4

3

2

1

0