3 high-impedance mode, 4 master and slave timing, Section 4.6.3 – Cirrus Logic CS53L30 User Manual

Page 26: Cs53l30

26

DS992F1

CS53L30

4.6 Serial Ports

4.6.3

High-Impedance Mode

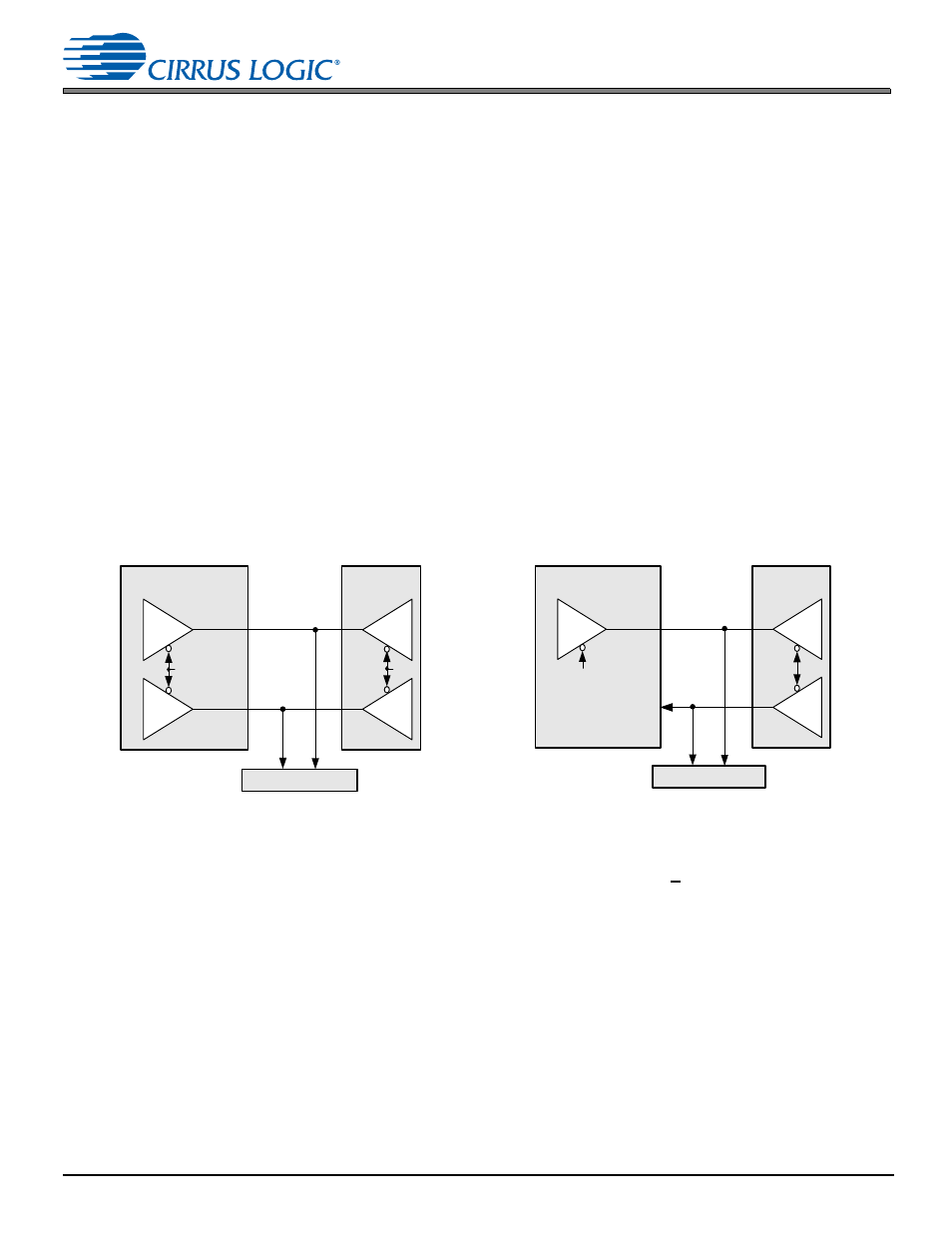

The serial port may be placed on a clock/data bus that allows multiple masters, without a need for external buffers. The

ASP_3ST bit places the internal buffers for the serial port interface signals in a high-impedance state, allowing another

device to transmit clocks and data without bus contention. If the CS53L30 serial port is a timing slave, its ASP_SCLK and

ASP_LRCK/FSYNC I/Os are always inputs and are thus unaffected by the ASP_3ST control.

In Slave Mode, setting ASP_3ST tristates the ASP_SDOUTx pins. In Master Mode, setting ASP_3ST tristates the ASP_

SCLK, ASP_LRCK/FSYNC, and ASP_SDOUTx pins. Before setting an ASP_3ST bit, the associated serial port must be

powered down and must not be powered up until the ASP_3ST bit is cleared. Below is the recommended tristate

sequence.

Sequence for initiating tristate:

1. Set the ASP_SDOUT1_PDN and ASP_SDOUT2_PDN bits.

2. If the ASP is in TDM Mode, set the ASP_TDM_PDN bit.

3. Set the ASP_3ST bit.

Sequence for removing tristate:

1. Clear the ASP_3ST bit.

2. If TDM Mode is desired, clear the ASP_TDM_PDN bit.

3. Clear the ASP_SDOUT1_PDN and ASP_SDOUT2_PDN bits.

show serial port interface busing for master and slave timing serial-port use cases.

4.6.4

Master and Slave Timing

Serial ports can independently operate as the master of timing or as a slave to another device’s timing. When mastering,

ASP_SCLK and ASP_LRCK/FSYNC are outputs; when slaved, they are inputs. ASP_M/S determines the Master/Slave

Mode.

In Master Mode, ASP_SCLK and ASP_LRCK/FSYNC clock outputs are either derived from the internal MCLK or taken

directly from its source, MCLK.

lists supported interface sample rates (Fs

ext

) for each supported MCLK and documents how to program the

registers to derive the desired Fs

ext

.

Figure 4-9. Serial Port Busing when Master Timed

Figure 4-10. Serial Port Busing when Slave Timed

CODEC Interface

Transmitting Device

#1

Transmitting

Device #2

Receiving Device

ASP_SDOUTx

ASP_SCLK,

ASP_LRCK

ASP_3ST

Transmitting

Device

#2

CODEC Interface

Transmitting Device

#1

ASP_SDOUTx

ASP_SCLK,

ASP_LRCK

ASP_3ST

Receiving Device