2 register e5hs1 gpi mask, 3 register e6hs1 tach mask, 2 register e5h – Rainbow Electronics LM93 User Manual

Page 81: S1 gpi mask, 3 register e6h, S1 tach mask, 0 registers

16.0 Registers

(Continued)

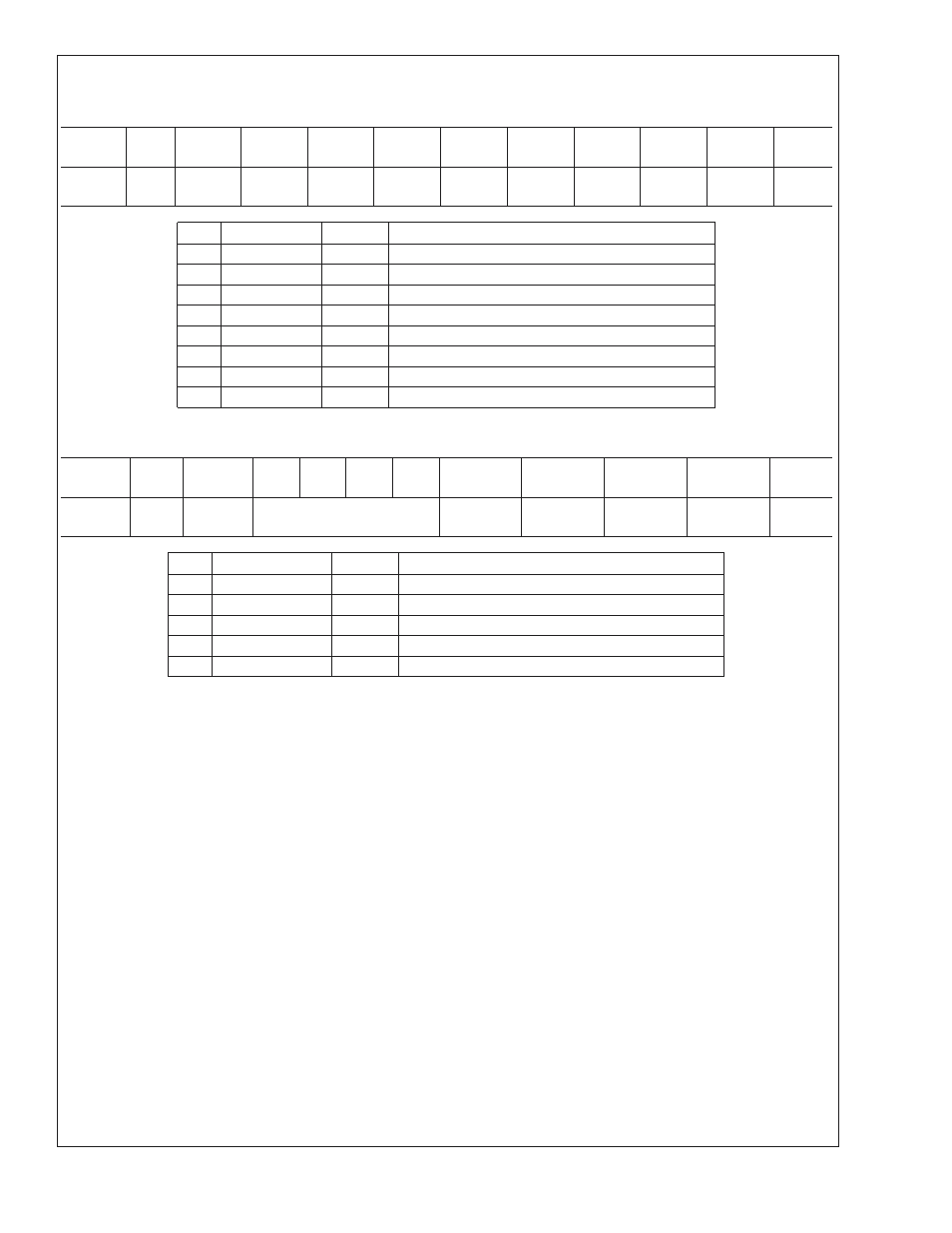

16.9.2 Register E5h

S1 GPI Mask

Register

Address

Read/

Write

Register

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Default

Value

E5h

R/W

S1 GPI

Mask

GPI7_S1

_MSK

GPI6_S1

_MSK

GPI5_S1

_MSK

GPI4_S1

_MSK

GPI3_S1

_MSK

GPI2_S1

_MSK

GPI1_S1

_MSK

GPI0_S1

_MSK

FFh

Bit

Name

R/W

Description

0

GPI0_S1_MSK

R/W

If set, GPI0 errors are masked in S1 sleep state.

1

GPI1_S1_MSK

R/W

If set, GPI1 errors are masked in S1 sleep state.

2

GPI2_S1_MSK

R/W

If set, GPI2 errors are masked in S1 sleep state.

3

GPI3_S1_MSK

R/W

If set, GPI3 errors are masked in S1 sleep state.

4

GPI4_S1_MSK

R/W

If set, GPI4 errors are masked in S1 sleep state.

5

GPI5_S1_MSK

R/W

If set, GPI5 errors are masked in S1 sleep state.

6

GPI6_S1_MSK

R/W

If set, GPI6 errors are masked in S1 sleep state.

7

GPI7_S1_MSK

R/W

If set, GPI7 errors are masked in S1 sleep state.

16.9.3 Register E6h

S1 Tach Mask

Register

Address

Read/

Write

Register

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Default

Value

E6h

R/W

S1 Tach

Mask

RES

TACH4_S1

_MSK

TACH3_S1

_MSK

TACH2_S1

_MSK

TACH1_S1

_MSK

0Fh

Bit

Name

R/W

Description

0

TACH1_S1_MSK

R/W

If set, Tach1 errors are masked in S1 sleep state.

1

TACH2_S1_MSK

R/W

If set, Tach2 errors are masked in S1 sleep state.

2

TACH3_S1_MSK

R/W

If set, Tach3 errors are masked in S1 sleep state.

3

TACH4_S1_MSK

R/W

If set, Tach4 errors are masked in S1 sleep state.

7:4

RES

R

Reserved

LM93

www.national.com

81