0 smbus interface – Rainbow Electronics LM93 User Manual

Page 23

14.0 SMBus Interface

(Continued)

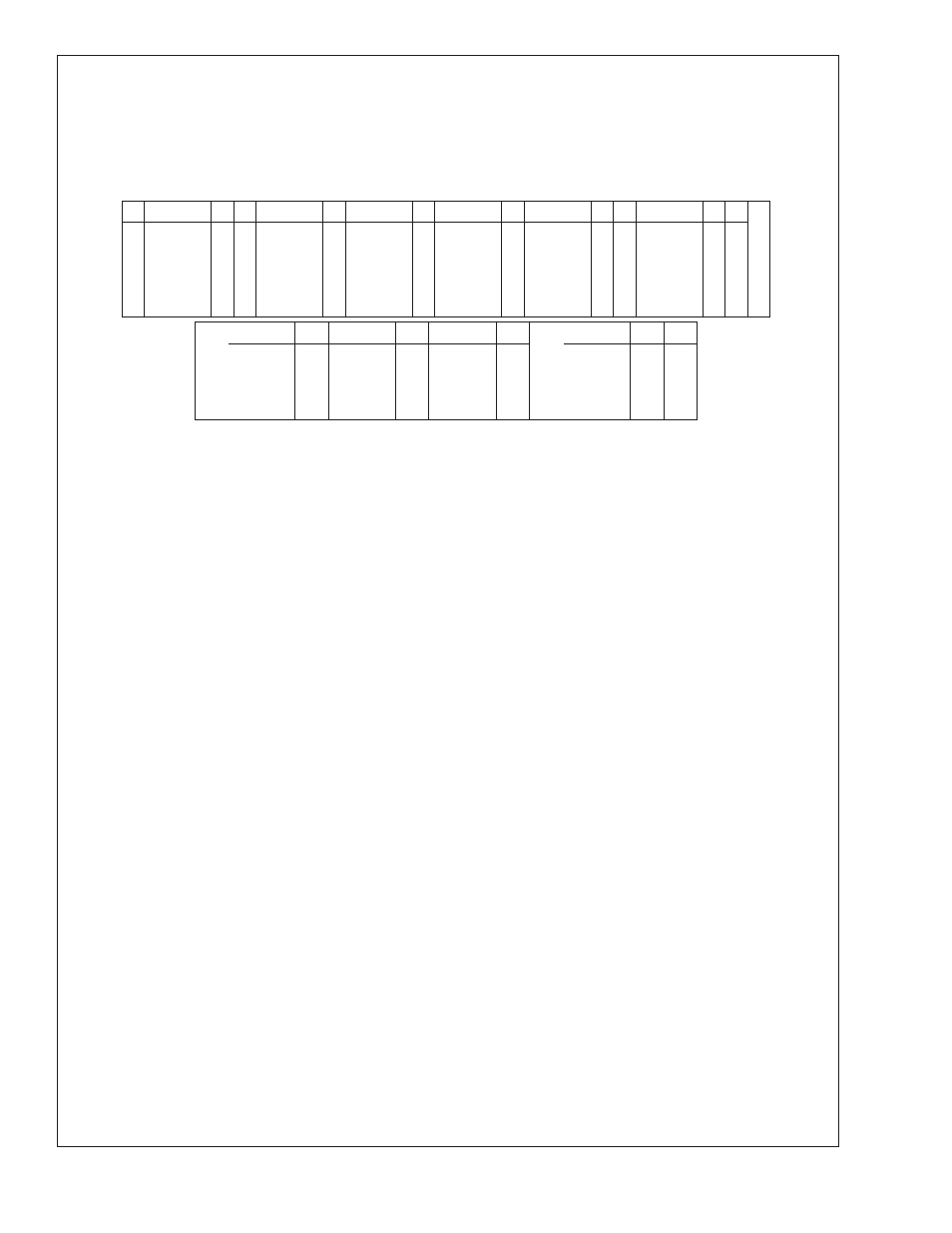

12. The master receives byte 1 and then asserts ACK.

13. The master receives byte 2 and then asserts ACK.

14. The master receives N-3 data bytes, and asserts ACK for each one.

15. The master receives data byte N and asserts a NACK.

16. The master asserts a STOP condition to end the transaction.

1

2

3

4

5

6

7

8

9

10

S

Slave

Address

W A

Block

Read

Command

Code

(F1h)

A

Byte

Count

(2h)

A

Start

Register

Address

A

Byte

Count

(1–20h)

(N)

A

S

Slave

Address

R

A

A

11

12

13

14

15

15

16

A

Byte

Count

(1–20h)

(N)

A

Data

Byte 1

A

Data

Byte 2

A

A

Data

Byte N

/A

P

Special Notes:

1.

The LM93 returns 00h when address locations outside of normal address space are read.

2.

Block reads do not wrap around from address FFh to 00h

3.

If the master acknowledges more bytes that it requested, the LM93 continues to supply data until the master does not

acknowledge a byte.

4.

If the master does not acknowledges a byte to prematurely abort a block read, the LM93 gets off the bus to allow the master

to issue a STOP signal.

LM93

www.national.com

23